#### Ionizing Radiation and Electromagnetic Interference on Integrated Circuits: from the need of combined test to current solutions

Fabian Vargas

IHP - Microelectronics Germany

vargas@ihp-microelectronics vargas@computer.org

Leibniz Institute for high performance microelectronics

Session 3 Meeting room: Carmen de la Victoria 10:25 - 10:55

## **Current State-of-the-Art**

From the best of our knowledge ...

Only a few works addressing the problem: trying to understand and quantify the combined effects of ionizing (**total-ionizing dose: TID**) and non-ionizing (**EMI**) radiations on ICs

IEEE TRANS. ON PLASMA SCIENCE, VOL. 40, NO. 6, JUNE 2012

Lack of research focusing on the combined effects of ionizing (**soft errors in memory elements**) and non-ionizing (**EMI**) radiations on ICs

#### Absence of a standard to rule combined tests

currently, only a Draft Recommendation from ITU:

"Overview of particle radiation effects on telecommunications systems", Geneva, Oct. 2016

Our studies have shown a **considerable reliability degradation** for systems operating in harsh environments (such as space, where satellite electronics is exposed to the combined effects of ioninzing rad: TID/soft errors and EMI) (*Analysis of SRAM-Based FPGA SEU Sensitivity to Combined EMI and TID-Imprinted Effects, IEEE TRANS. ON NUCLEAR SCIENCE, VOL. 63, JUNE 2016*)

## Where is the problem?

It is a common practice that ...

engineers qualify electronic systems to EMI, TID or SEU, or eventually to all of them, but often NOT taking into account the combined effects one phenomenon may take over the other.

e.g., assume a given part of an embedded system for satellite application is certified by a set of EMI tests according to specific stds

## Where is the problem?

Who can ensure that time, art will still per same set of EMI stds, after a given l cumulated over time on the system, if for EMI and radiation?

operly according to the TID radiation has been as certified independently

Moreover, who can ensure that the system will be approved for the same set of EMI stds, if operating in a bareh environment with dense flux of high-energy particles (SEEs)?

## **Our Contribution**

**Aerospace Industry**

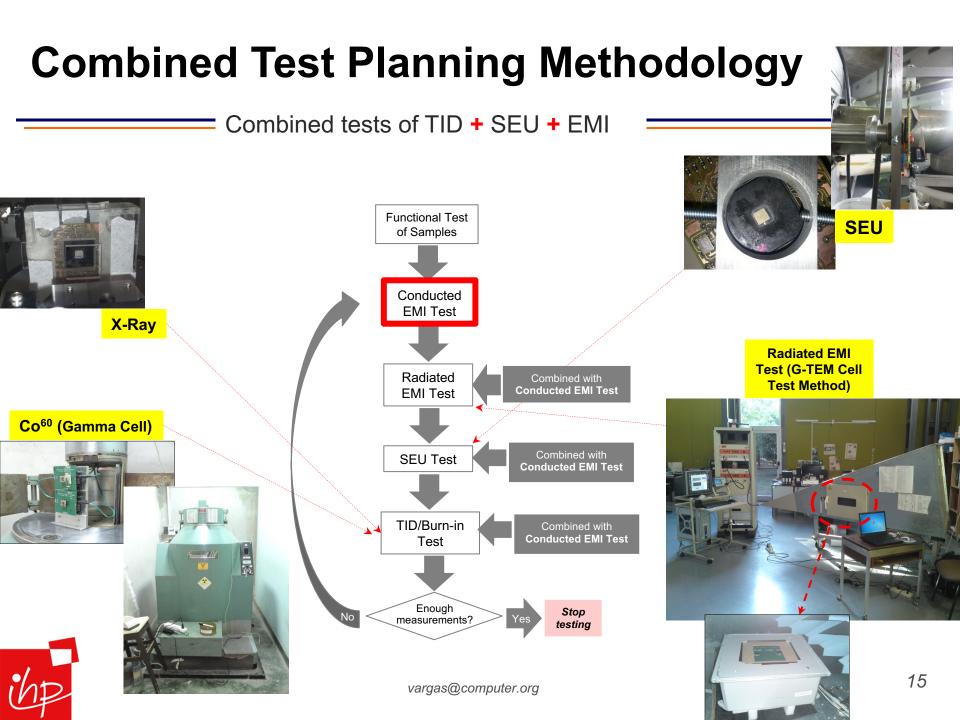

## Develped technology to qualify ICs for the Brazilian Space Agency having in mind combined effects of TID, SEU and EMI

## Study: addressing FPGAs of different types and technology nodes

## **Our Contribution**

The analyzed FPGAs ...

Xilinx: Spartan3XC3S500E Virtex4XC4VFX12-10SF363 (SRAM) Microsemi: ProAsic3E1500 (Flash) IECAS: ERC3000-G (SRAM)

## **Our Contribution**

We .... analyzed the impact of combined tests for EMI + radiation (TID/SEU) on the reliability of electronic components proposed a new methodology that takes this combination into account in order to qualify state-of-the-art COTS ICs

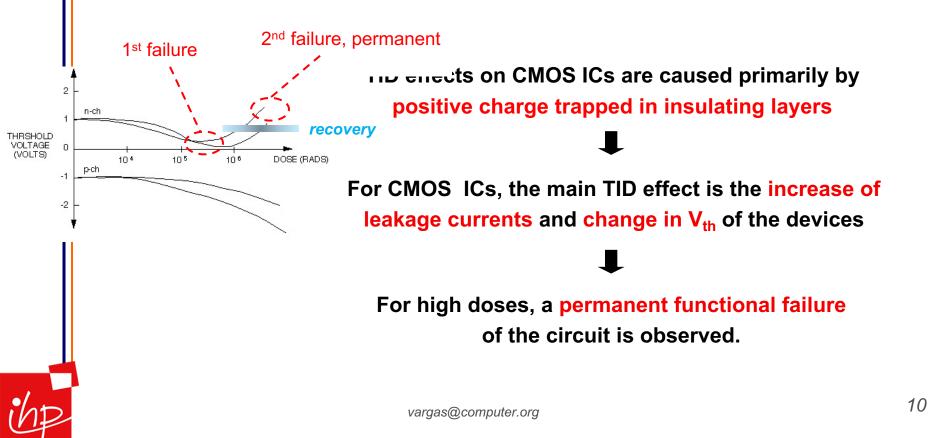

For critical applications (military, aerospace or biomedical) reliability assurance to total ionizing dose (TID) radiation is always at a premium being a key-issue for the success of such products in the market.

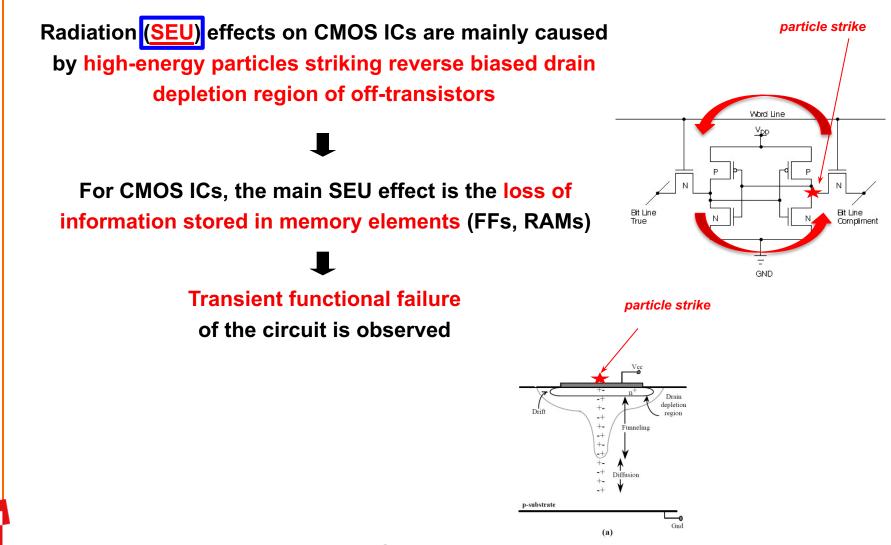

## Understanding the Effects of Radiation (SEE) on Electronics

vargas@computer.org

Fig. 1. Illustration of the charge collection mechanism that cause single-event upset: (a) particle strike and charge generation; (b) current pulse shape generated in the n+p junction during the collection of the charge.

Radiation (SET) effects on CMOS ICs are mainly caused by high-energy particles striking logic along with critical paths For CMOS ICs, the main <u>SET</u> effect is the loss of information stored in memory elements (FFs, RAMs) Transient functional failure of the circuit is observed particle strike  $AD(\overline{B \oplus C})$

$\overline{A + D} = \overline{A}\overline{D}$

The increasing hostility of the electromagnetic environment caused by the widespread adoption of electronics, (mainly wireless technologies), represents a huge challenge for the reliability of RT embedded systems.

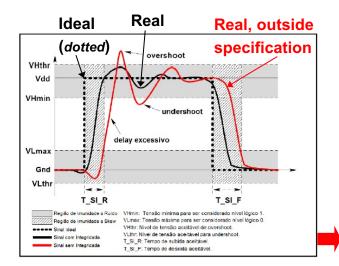

Electromagnetic Interference (EMI) Power Supply Disturbances (PSD) Transient Faults

Signals outside noise margins can be erroneously interpreted and stored by memory elements at the end of critical paths

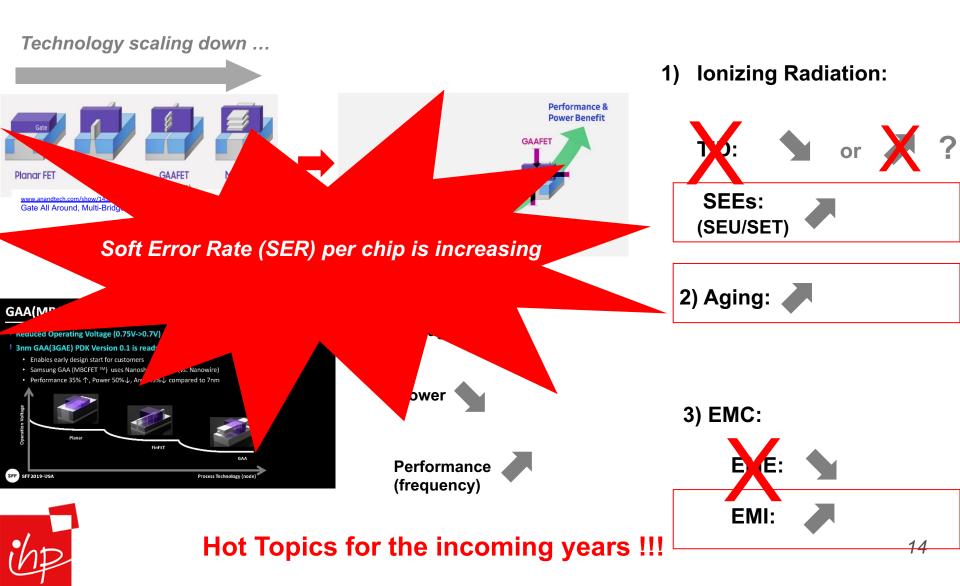

## **Technology trends impact on ICs**

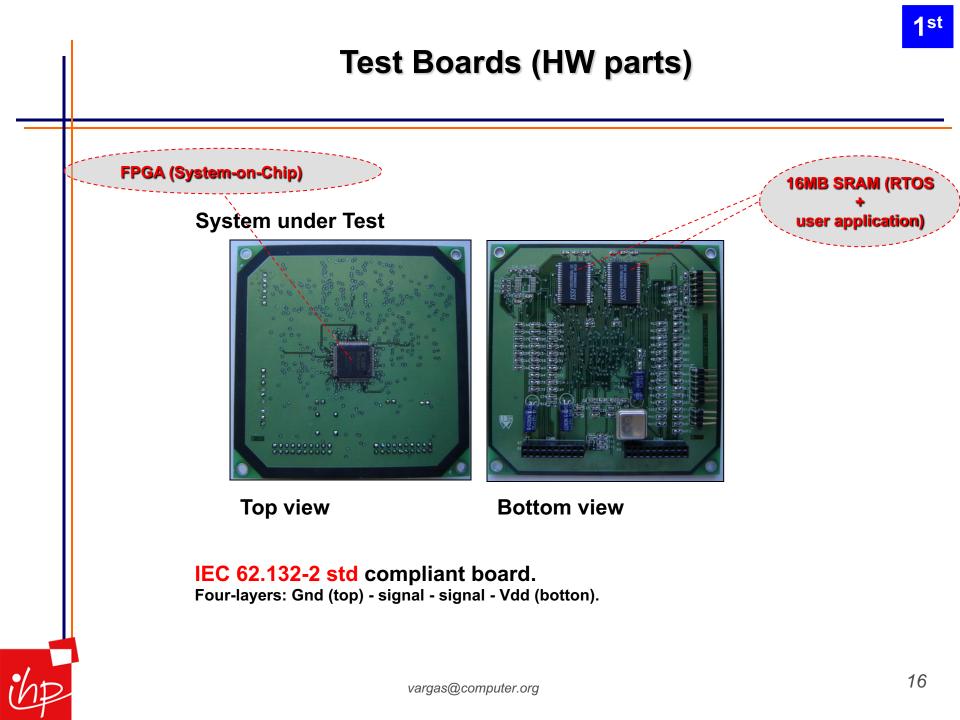

## **Test Boards (HW parts)**

1 st

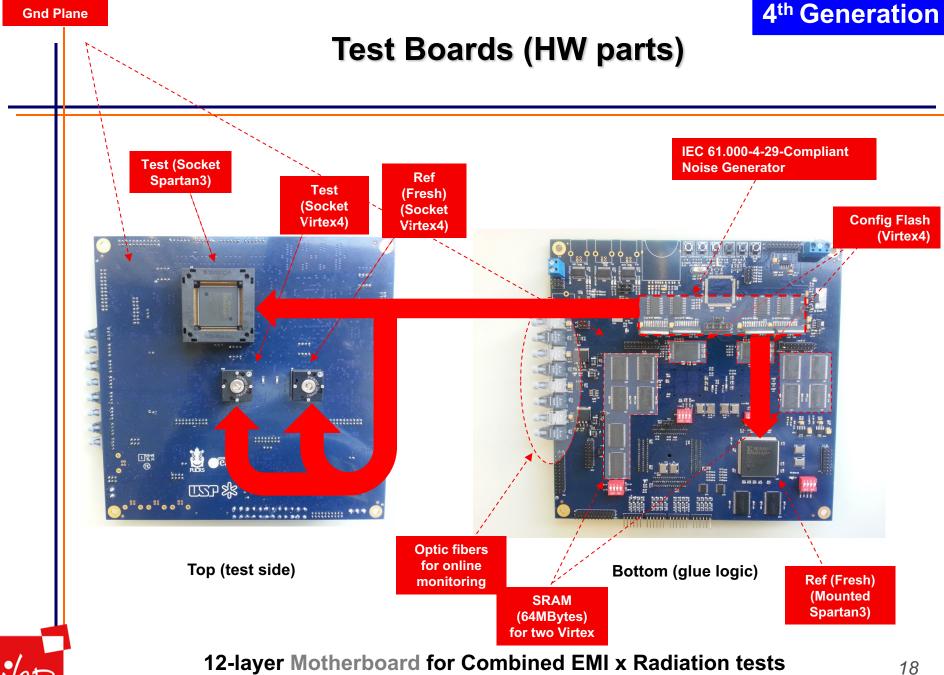

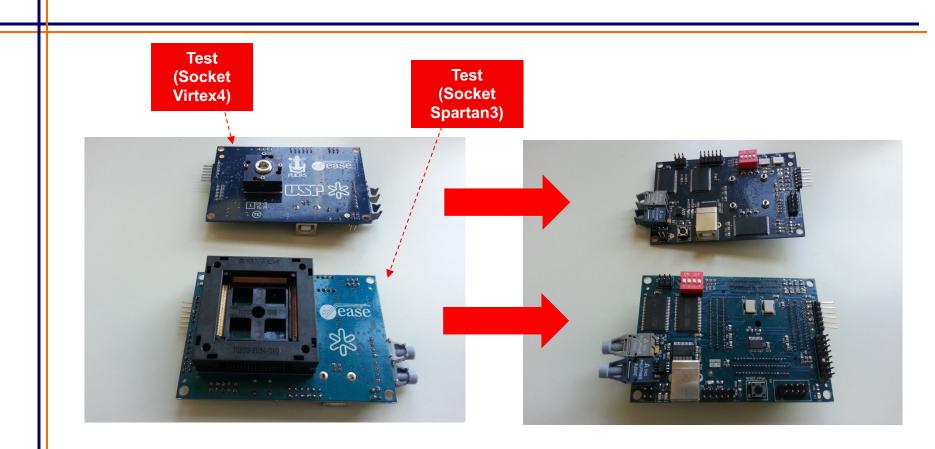

#### 4<sup>th</sup> Generation

## **Test Boards (HW parts)**

Top (test side)

**Bottom (glue logic)**

#### 6-layer Daughterboards for Combined EMI x Radiation tests

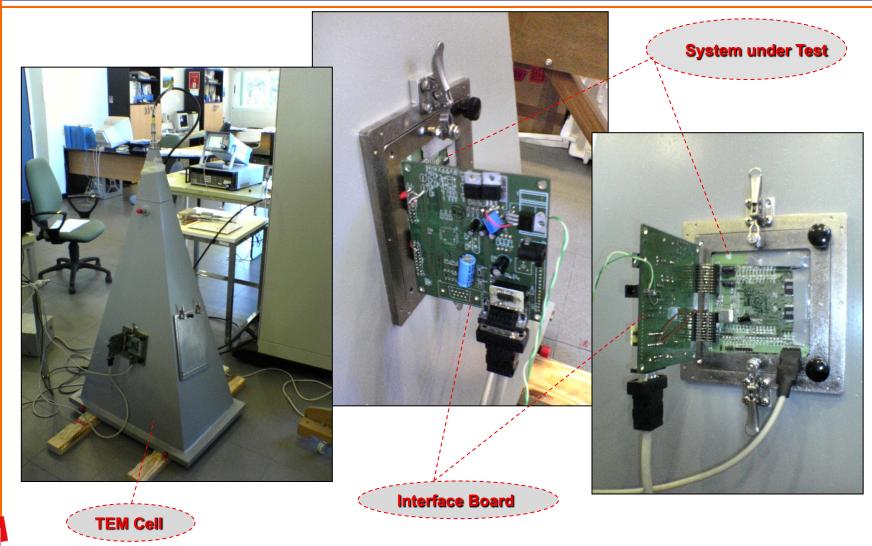

## **Experiment (1)**

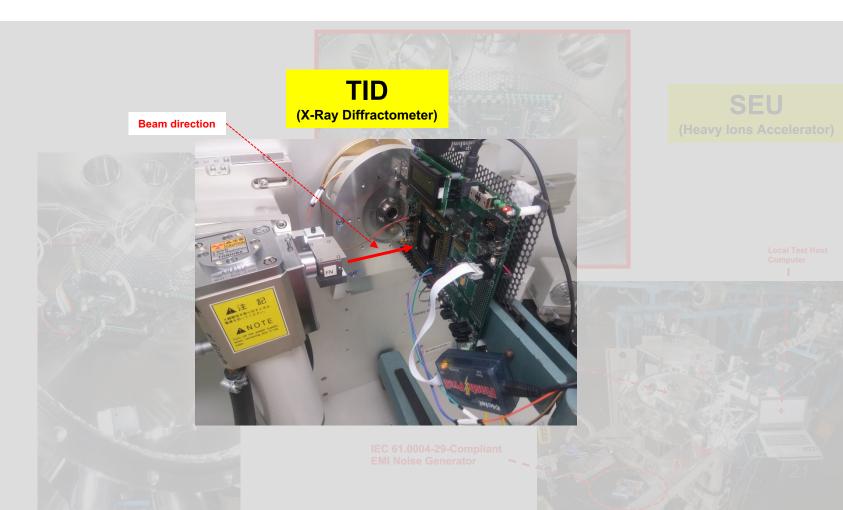

# Combined Tests: Conducted EMI + TID + SEU

ath

Photo with Microsemi ProAsic3E A3PE1500

**Experiment (1)**

#### **Goal** (Xilinx Spartan3 XC3S500E):

SEU sensitivity w.r.t. Conducted Noise on V<sub>DD</sub> Bus, TID and Imprint Effect

## **Experiment (1)**

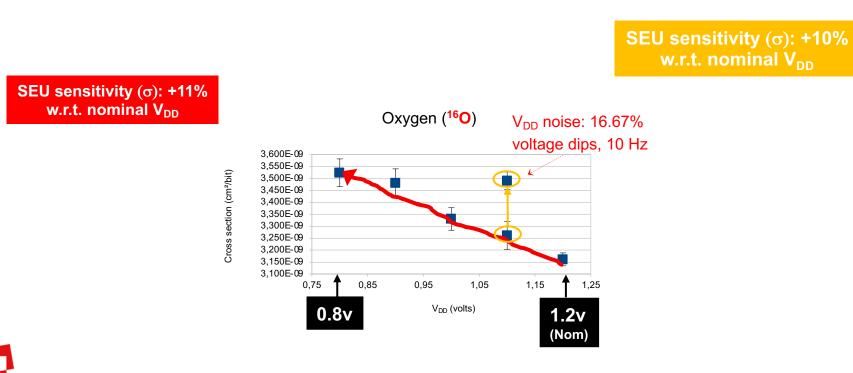

$\label{eq:configuration Bitstream} \mbox{(Configuration Bitstream)} \mbox{ Cross Section as function of Power Supply (V_{DD}) Disturbance (Fresh FPGA)}$

## **Experiment (1)**

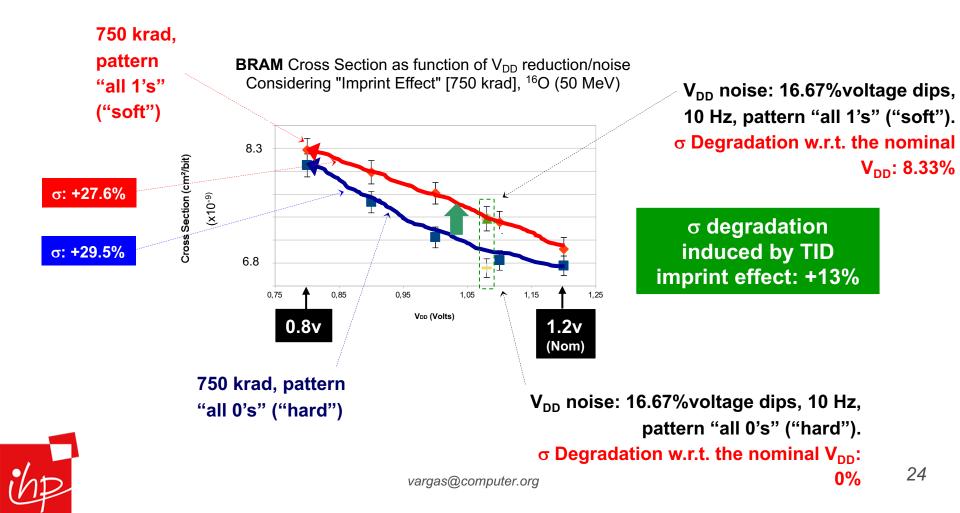

## **Imprint Effect:**

When a memory element remains for a long period storing **the same logical value** ("0" or "1") while being irradiated for high dose rates, it **tends to maintain this value during the rest of its lifetime** (similar to the "**stuck-at fault**" **Model** widely used by industry).

We have deposited **750 krad** and **950 krad** on two **Xilinx/Spartan3** FPGAs storing the pattern "all 0's" in the BRAMs ("hard" pattern) (same fabrication lot)

## **Experiment (1)**

(<u>BRAM</u>) Cross Section as function of Power Supply (V<sub>DD</sub>) Disturbance (**Irradiated FPGA with 750 krad**)

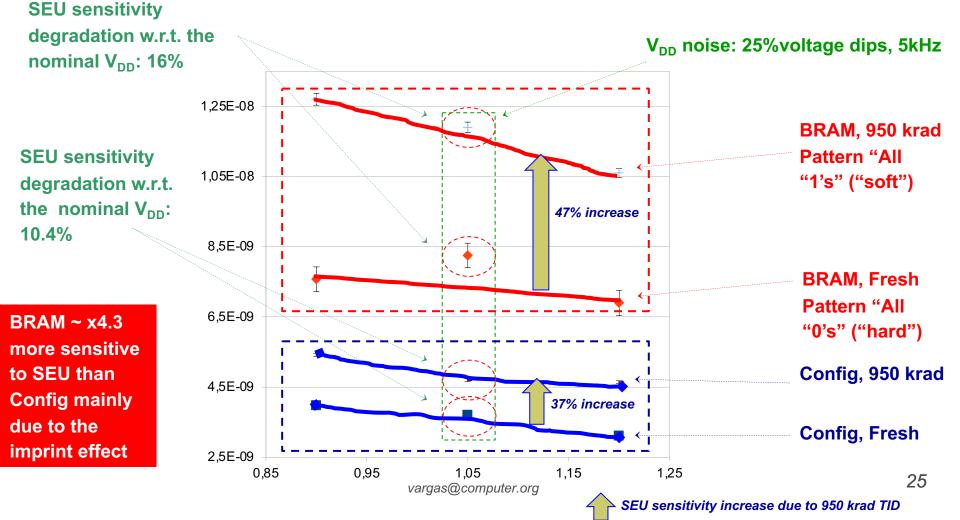

## **Experiment (1)**

(<u>BRAM vs. Config</u>) Cross Section as function of Power Supply (V<sub>DD</sub>) Disturbance (Irradiated FPGA with 950 krad, <sup>28</sup>Si)

## **Experiment (1)**

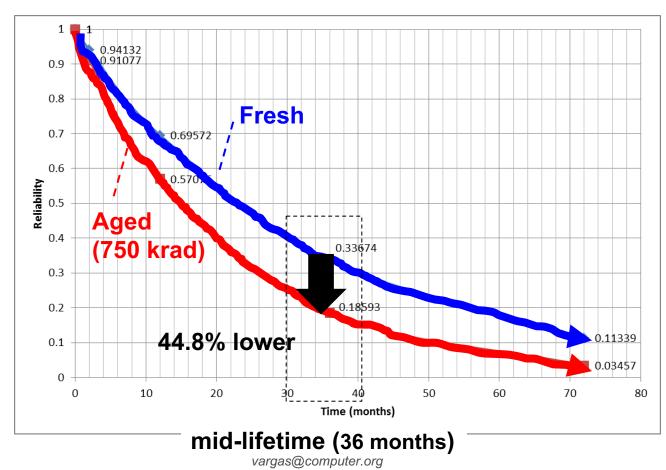

#### **BRAM Reliability per Bit**

Power Supply (V<sub>DD</sub>): 0.85 volts SEU Results for Fast Neutrons (<sup>241</sup>AmBe), [2 – 11] MeV (**Fresh x Irradiated FPGA with 750 krad, <sup>28</sup>Si**)

Mainly induced by the "soft" pattern (all 1's)

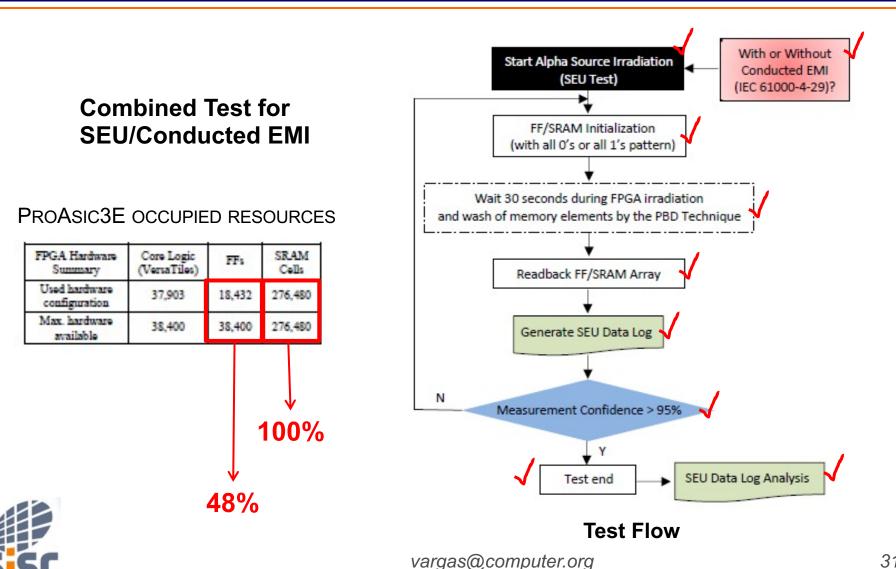

# Combined Tests: Conducted EMI + SEU

#### Microsemi ProAsic3E A3PE1500

## **Experiment (2)**

#### Microsemi ProAsic3E A3PE1500 FPGA:

- (a) Packaged device;

- (b) Unpacked, ready for radiation (SEU and TID) tests.

(commonly used for automotive and aerospace apps)

## **Experiment (2)**

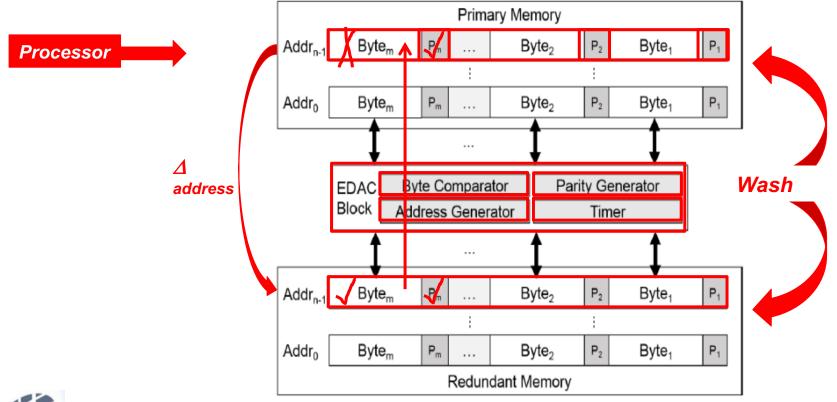

## Parity per Byte & Duplication (PBD) EDAC Technique

General block diagram of the proposed EDAC approach.

vargas@computer.org

#### Microsemi ProAsic3E A3PE1500

## **Experiment (2)**

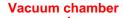

#### **SEU Test:**

## ProASIC3E FPGA exposed to 5.4 MeV alpha particles emitted by a <sup>241</sup>Am source

Alpha-particle flux:. Appr. 1,300 part/cm<sup>2</sup>.s (13.7 particles/second /millisteradian)

**Fig. 5.** Test setup for the <sup>241</sup>Am source

FPGA under test

vargas@computer.org

#### Microsemi ProAsic3E A3PE1500

## **Experiment (2)**

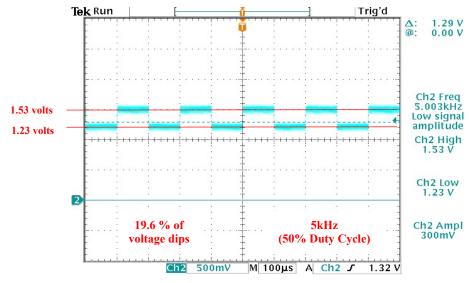

## **Experiment (2)**

**EMI Test:**

Fault injection campaigns were generated according to the IEC 61000-4-29 Std

Voltage dips applied to the FPGA core  $V_{DD}$  pins (Nominal core  $V_{DD}$ : 1.5 volts)

IC peripheries remained fixed at their nominal voltage levels (3.3, 2.5 and 1.8 volts)

**Fig. 6.** Noise injected on FPGA  $V_{DD}$  pins.

vargas@computer.org

#### Microsemi ProAsic3E A3PE1500

## **Experiment (2)**

#### **Obtained Results**

TABLE II.

#### CAPABILITY OF THE PBD TECHNIQUE TO MITIGATE SOFT ERRORS INDUCED BY ALPHA PARTICLES, <u>WITH AND WITHOUT CONDUCTED EMI NOISE</u> ON THE CORE INPUT POWER PORT OF THE FPGA. RESULTS FOR THE <u>SRAM</u> ARRAY.

| Average number of                    | Without<br>Noise | With<br>Noise | Soft Error<br>Increase |

|--------------------------------------|------------------|---------------|------------------------|

| observed bit-flips                   | 395.00           | 1,049.00      | 2.7                    |

| bit-flips per memory bits            | 0.0027           | 0.0071        | 2.6                    |

| bit-flips per second                 | 0.4760           | 1.0708        | 2.3                    |

| bit-flips per memory bits per second | 0.0028           | 0.0073        | 2.6                    |

| addresses corrected**                | 393.33           | 1,044.37      | 2.7                    |

| addresses not corrected              | 0.17             | 0.63          | 3.7                    |

| masked addresses ***                 | 0                | 0             | 0                      |

| EDAC Effectiveness (%)               | 99.96            | 99.94         |                        |

\*"Soft Error Increase" rate computed as: With Noise/Without Noise.

<sup>\*\*</sup>the number of addresses corrected is smaller than the number of observed bit-flips because there was at least one address with more than one bit flip.

<sup>\*</sup>masked addresses are addresses not detected and not corrected, thus escaping detection by the proposed technique.

#### Microsemi ProAsic3E A3PE1500

#### **Experiment (2)**

**Obtained Results**

## Compared to only ionizing radiation, when the IC was additionally exposed to conducted EMI, FF & SRAM arrays became ~ 2.7 times more sensitive to soft errors

## Thank you for your attention ...