## Memristive In-Memory-Computing: Radiation hard Memory for Computing in Space (MIMEC)

ELICSR Training School – Granada, Spain

Emilio Perez-Bosch Quesada, Tommaso Rizzi, Eduardo Perez, Christian Wenger

26.10.2022

IHP – Leibniz-Institut für innovative Mikroelektronik

## Outline

| 1 | Introduction: memristors, RRAM and applications |

|---|-------------------------------------------------|

| 2 | MIMEC – goals and development                   |

| 3 | Radiation hardness – device level               |

| 4 | System level simulation - ECC                   |

| 5 | Outlook                                         |

|   |                                                 |

|   |                                                 |

|   |                                                 |

## Outline

| Introduction: memristors, RRAM and applications |

|-------------------------------------------------|

| MIMEC – goals and development                   |

| Radiation hardness – device level               |

| System level simulation - ECC                   |

| Outlook                                         |

|                                                 |

|                                                 |

|                                                 |

. . . . . . . . . . . . . . . . . .

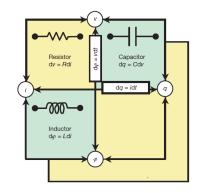

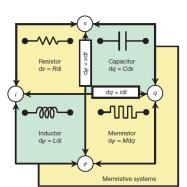

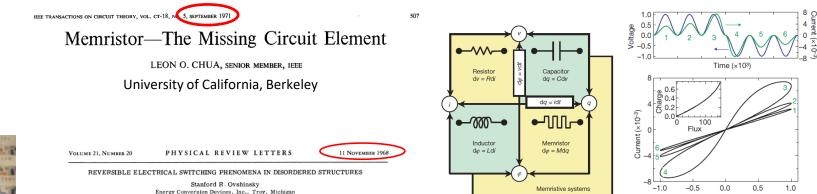

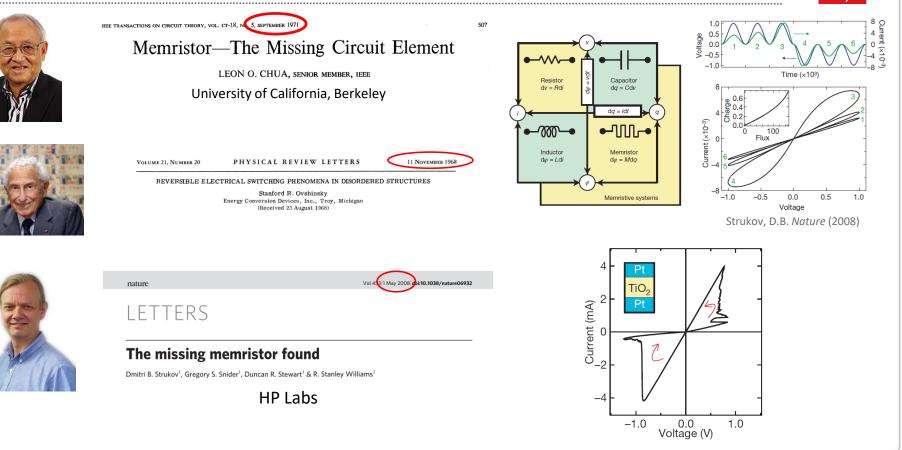

ieee transactions on circuit theory, vol. ct-18, N 5, september 1971

Memristor—The Missing Circuit Element

LEON O. CHUA, SENIOR MEMBER, IEEE University of California, Berkeley

507

Strukov, D.B. Nature (2008)

gy Conversion Devices, Inc., Troy, M (Received 23 August 1968)

Voltage Strukov, D.B. *Nature* (2008)

. . . . . . . . . . . . . . .

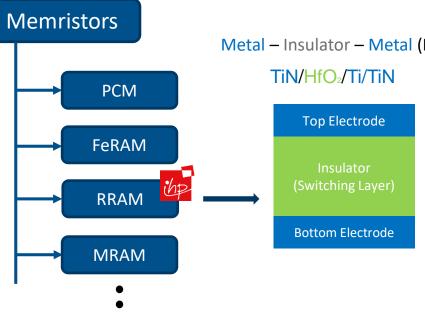

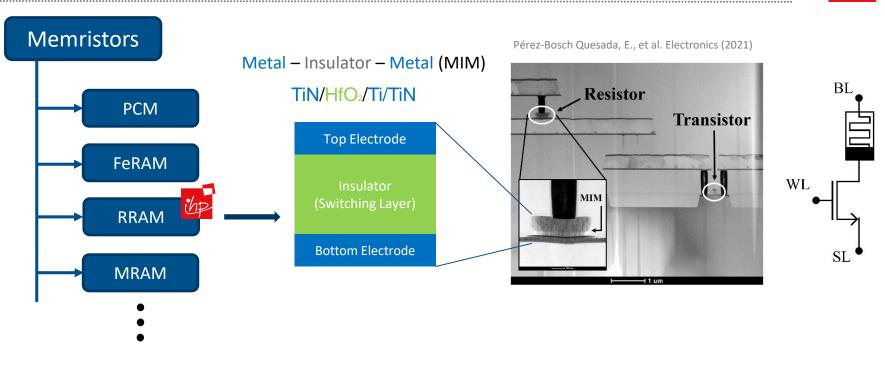

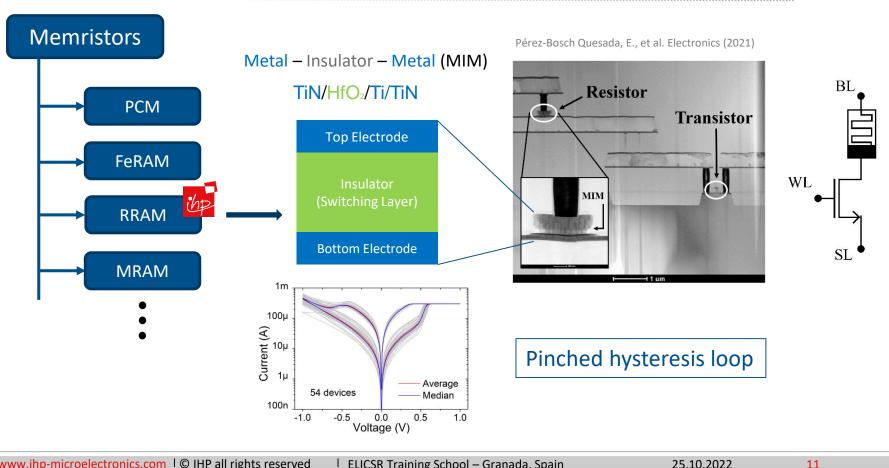

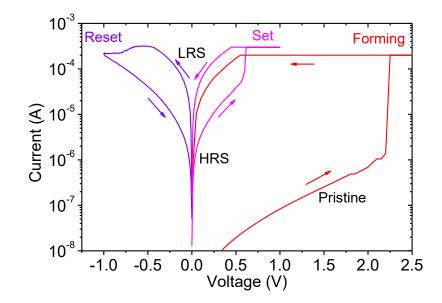

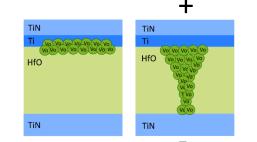

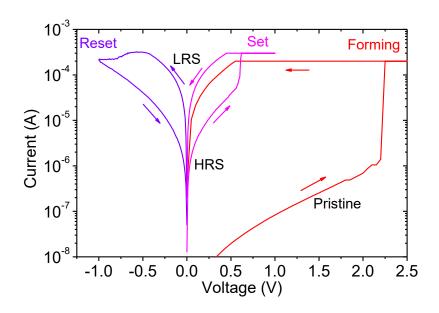

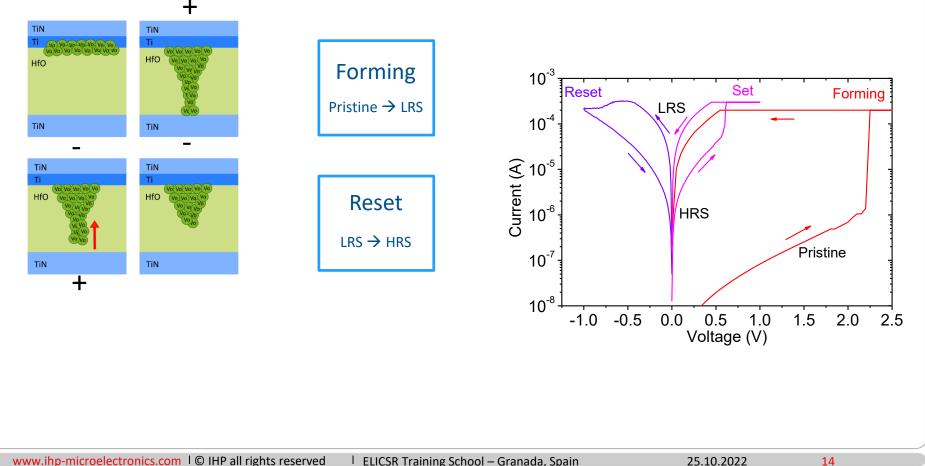

Metal – Insulator – Metal (MIM)

. . . . . . . . . . . .

.....

.....

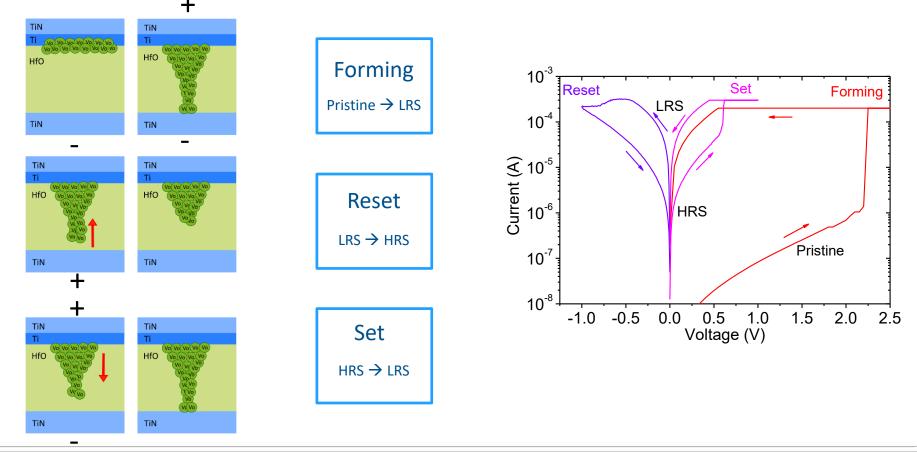

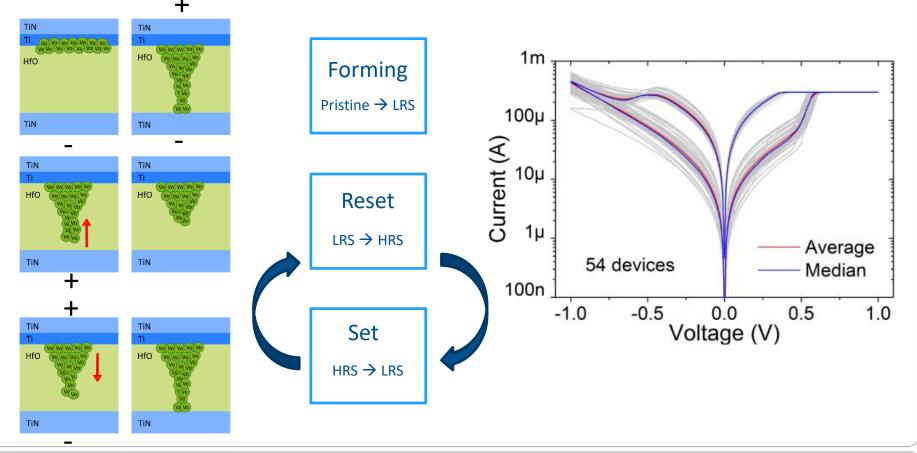

| Forming                    |

|----------------------------|

| Pristine $\rightarrow$ LRS |

ibp

.....

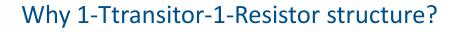

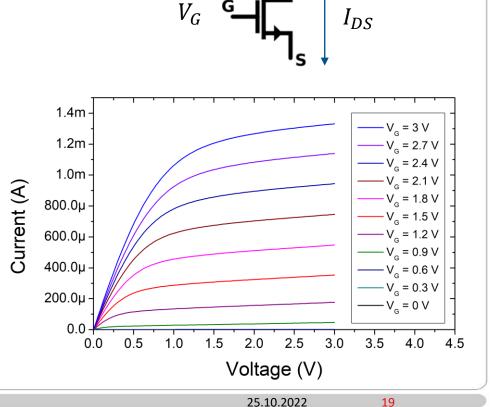

Why 1-Ttransitor-1-Resistor structure?

NMOS

Voltage (V)

### Why 1-Ttransitor-1-Resistor structure?

- Protects against current overshoots ۲

- Selector device in arrays

- MULTILEVEL CELL

NMOS

G

П

20

. . . . . . . . . . . . .

www.ihp-microelectronics.com | © IHP all rights reserved | ELICSR Training School – Granada, Spain

www.ihp-microelectronics.com | © IHP all rights reserved | ELICSR Training School – Granada, Spain

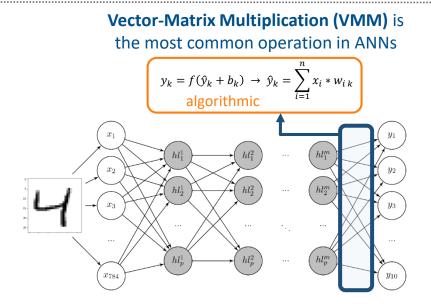

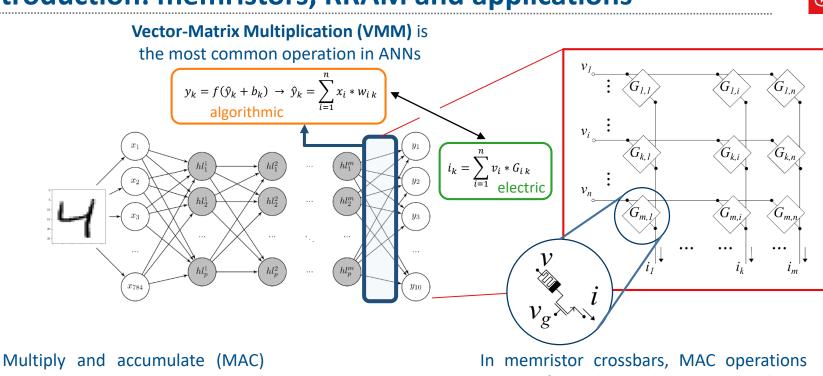

Multiply and accumulate (MAC) operations may require **several processing cycles** to be computed in traditional CPUs In memristor crossbars, MAC operations are performed simultaneously **utilizing Kirchhoff's current law and Ohm's law.**

Multiply and accumulate (MAC) operations may require **several processing cycles** to be computed in traditional CPUs In memristor crossbars, MAC operations are performed simultaneously **utilizing Kirchhoff's current law and Ohm's law.**

## Outline

| Introduction: memristors, RRAM and applications |

|-------------------------------------------------|

| MIMEC – goals and development                   |

| Radiation hardness – device level               |

| System level simulation - ECC                   |

| Outlook                                         |

|                                                 |

|                                                 |

|                                                 |

|                                                 |

Improve Internet access to rural and developing areas of the world.

- Noble Cause with high technical and optimization problems to solve

- Noble Cause with controversial and vivid discussion around it

27

Improve Internet access to rural and developing areas of the world.

• Noble Cause with high technical and optimization problems to solve

Improve Internet access to rural and developing areas of the world.

- Noble Cause with high technical and optimization problems to solve

- Noble Cause with controversial and vivid discussion around it

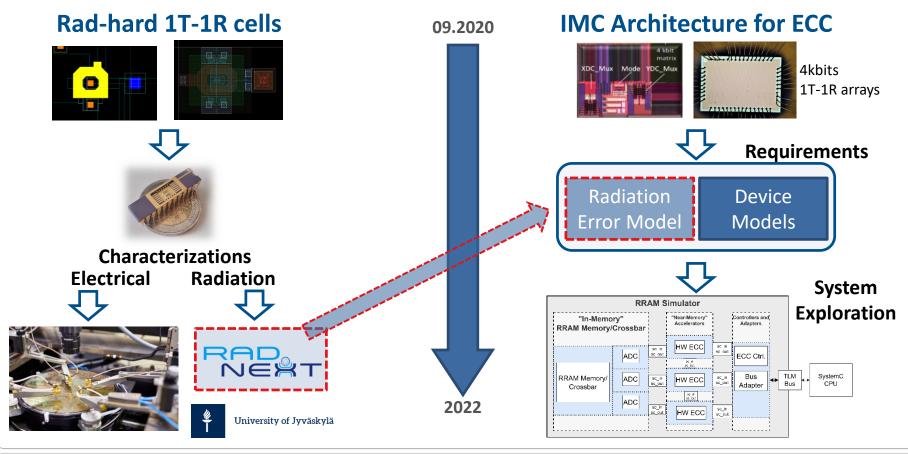

**MIMEC – goals and development**

Improve Internet access to rural and developing areas of the world.

Noble Cause with high technical and optimization problems to solve

# ibp

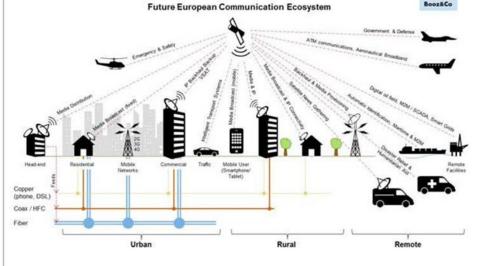

### Internet of Space (IoS) applications:

- Computation into space

- <u>Radiation hardened</u> (**Rad-Hard**) electronics

https://www.networld2020.eu/satcom-wg/

# Conceive, realize, prototype and evaluate a RRAM-based computing architectures for IoS applications

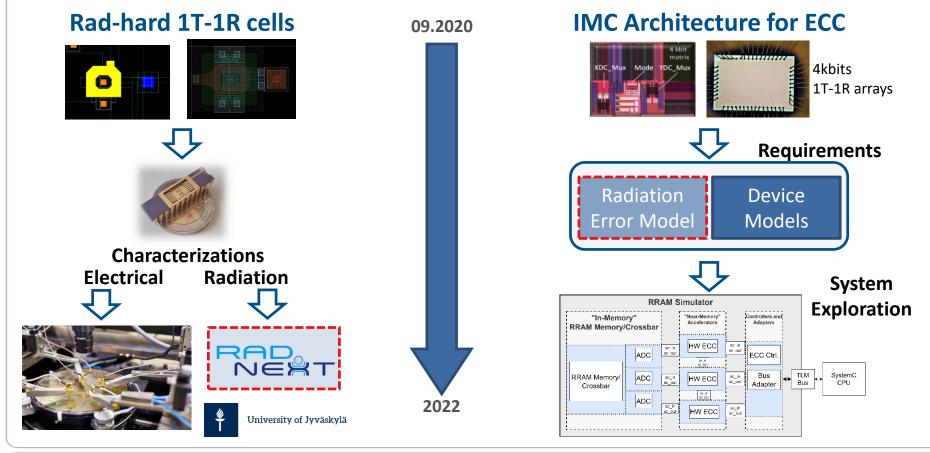

Radiation Hardened (Rad-hard) 1T-1R cells

In-memory computing (IMC) architecture for detection and correction of errors

www.ihp-microelectronics.com | © IHP all rights reserved | ELICSR Training School – Granada, Spain 26.10.2022 30

## **Project Timeline**

www.ihp-microelectronics.com © IHP all rights reserved ELICSR Training School – Granada, Spain

26.10.2022

## **Project Timeline**

www.ihp-microelectronics.com | © IHP all rights reserved | ELICSR Training School – Granada, Spain

26.10.2022

## Outline

| 1 | Introduction: memristors, RRAM and applications |

|---|-------------------------------------------------|

| 2 | MIMEC – goals and development                   |

| 3 | Radiation hardness – device level               |

| 4 | System level simulation - ECC                   |

| 5 | Outlook                                         |

|   |                                                 |

|   |                                                 |

|   |                                                 |

|   |                                                 |

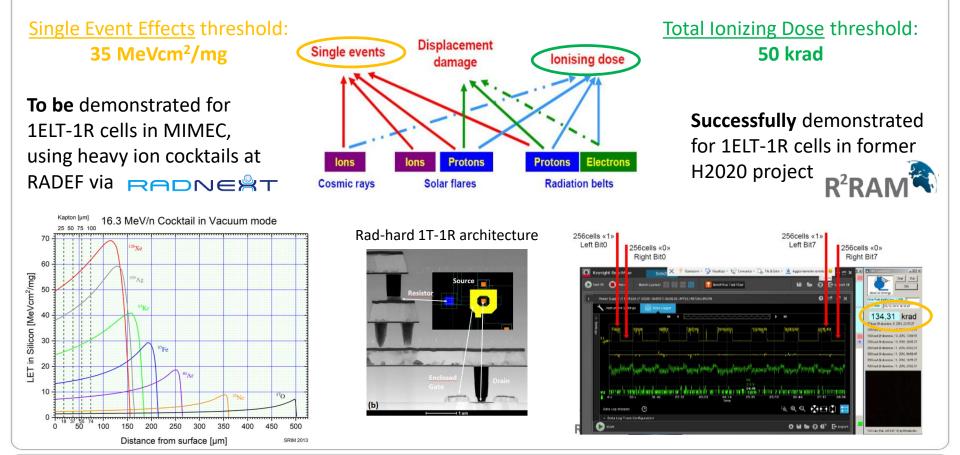

## Hardness requirements for satellites

www.ihp-microelectronics.com | © IHP all rights reserved

| ELICSR Training School – Granada, Spain

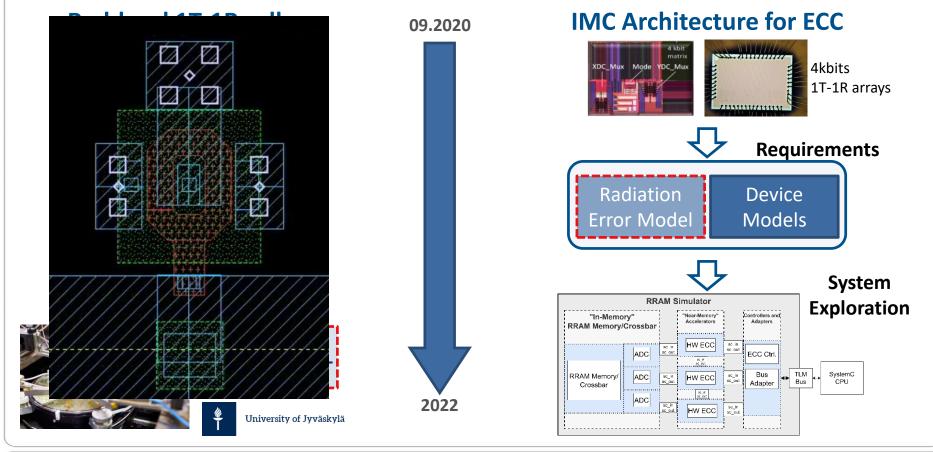

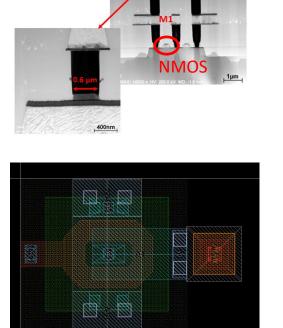

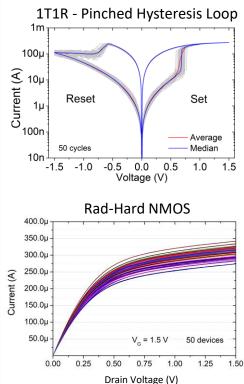

## Rad-Hard 1T1R design

- Standard 1T1R configuration

- MIM-Stack in BEOL → intrinsic resilient to radiation

- Selection Transistor in substrate  $\rightarrow$  prone to radiation

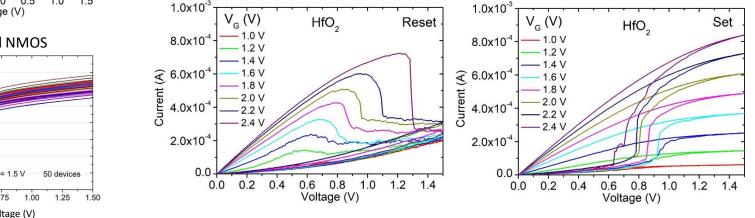

## Design of Rad-hard structure:

- MIM-Stack in BEOL  $\rightarrow$  intrinsic resilient to radiation

- ELT-NMOS (130 nm)  $\rightarrow$  TID robust

### Optimize transistor dimensions

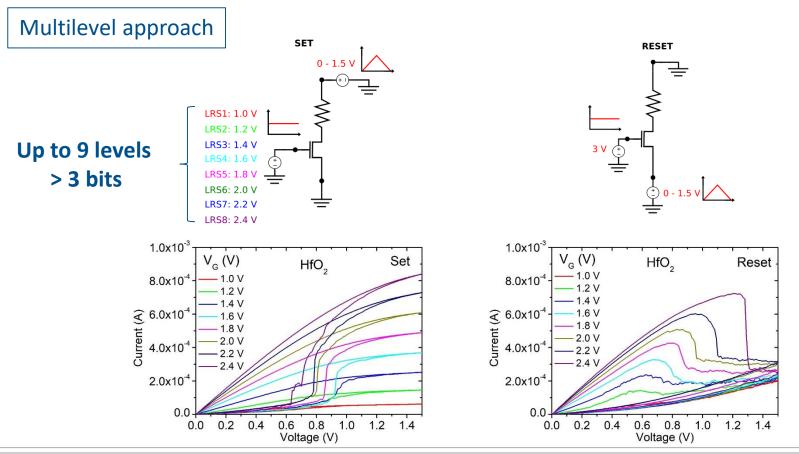

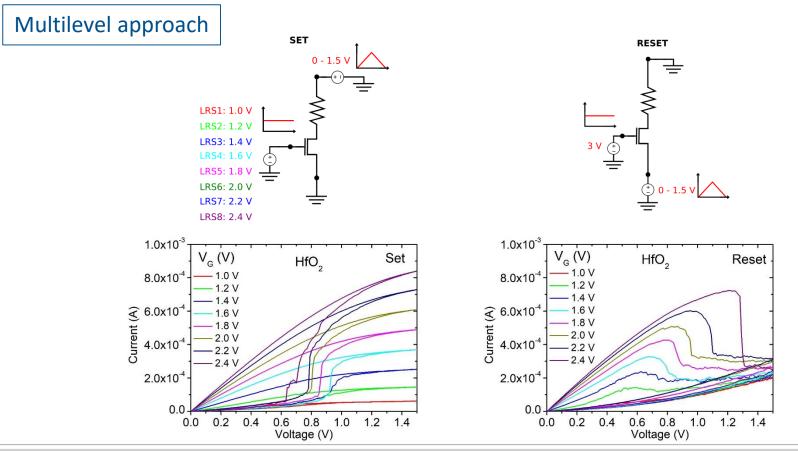

- Comparison with former measurements:

- Change of programming voltages

- Influence on multi-level operation

- Influence of layout arrangements

Βl

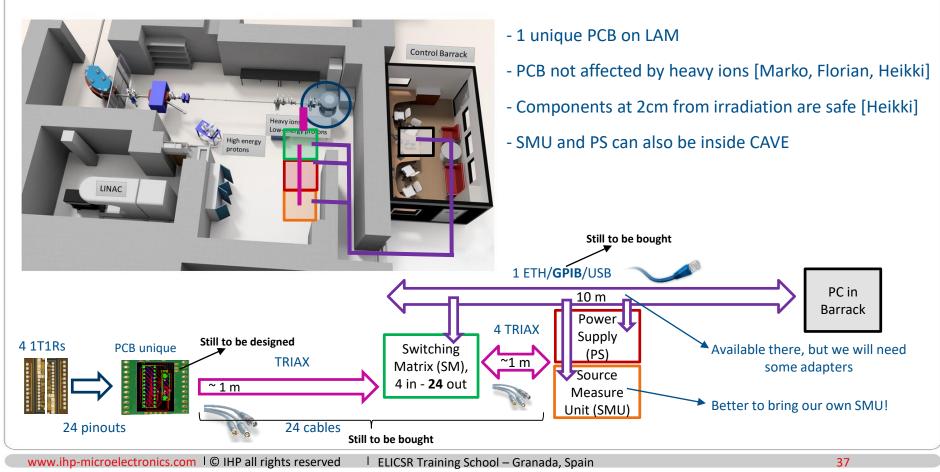

### **Electrical Characterization:**

### Package with opening for radiation test

### **Multilevel Switching:**

**Setup**

## Outline

| 1 | Introduction: memristors, RRAM and applications |

|---|-------------------------------------------------|

| 2 | MIMEC – goals and development                   |

| 3 | Radiation hardness – device level               |

| 4 | System level simulation - ECC                   |

| 5 | Outlook                                         |

|   |                                                 |

|   |                                                 |

|   |                                                 |

## **Project Timeline**

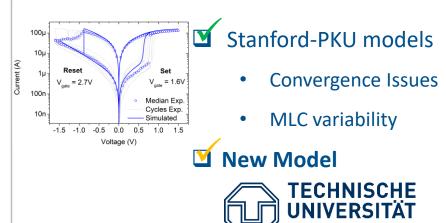

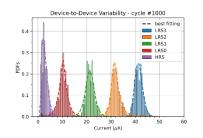

### The memristive model must be **fast** and **"accurate enough"** in circuit/system simulations.

### **Physical-based compact models**

- Reproduce switching mechanism

- Difficult to capture the variability

- Slow (for system level)

### **Gamma** Statistical behavioral models

- Reproduce stochastic nature

- Fast

- Difficult to capture the device's evolution

Develop Framework

Extract models for 4kbits arrays

RESDEN

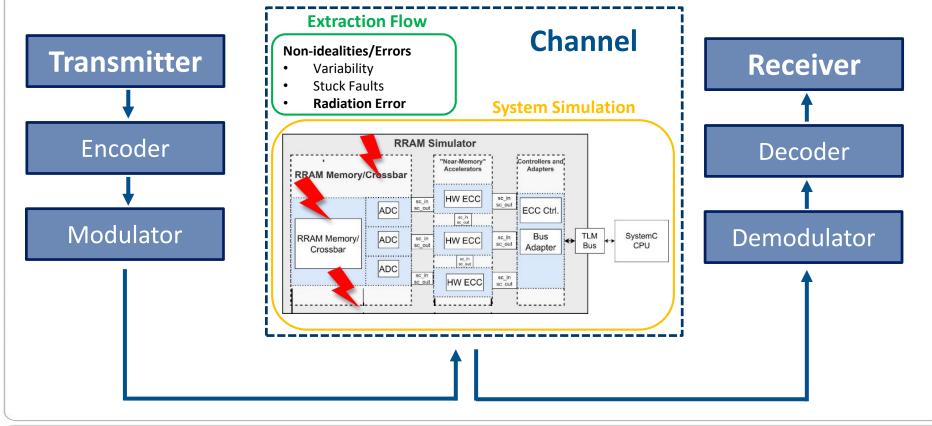

### **System Exploration**

## Outline

| 1 | Introduction: memristors, RRAM and applications |

|---|-------------------------------------------------|

| 2 | MIMEC – goals and development                   |

| 3 | Radiation hardness – device level               |

| 4 | System level simulation - ECC                   |

| 5 | Outlook                                         |

|   |                                                 |

|   |                                                 |

|   |                                                 |

|   |                                                 |

• RRAM technology inherently exhibit high radiation tolerance

- Multilevel capabilities open many design possibilities for IoS applications

- 1ELT-1R structure demonstrated good tolerance during TID tests

- SEE tolerance of 1ELT-1R structures will be tested in the near future

- Model development is on going

- RRAM simulator framework to optimize ECC

- RRAM-based computation systems to be deployed in radiation harsh environments

Reiser, D. *et al.* (2022). A Framework for Ultra Low-Power Hardware Accelerators Using NNs for Embedded Time Series Classification. J. Low Power Electron. Appl. 2022, 12, 2. <u>https://doi.org/10.3390/jlpea12010002</u>

Fritscher, M. *et al.* (2022). Mitigating the Effects of RRAM Process Variation on the Accuracy of Artificial Neural Networks. SAMOS 2021. Lecture Notes in Computer Science, vol 13227. Springer, Cham. <u>https://doi.org/10.1007/978-3-031-04580-6\_27</u>

Rizzi T. *et al.* (2021). Comparative Analysis and Optimization of the SystemC-AMS Analog Simulation Efficiency of Resistive Crossbar Arrays. *2021 XXXVI Conference on Design of Circuits and Integrated Systems (DCIS)*, 2021, pp. 1-6, https://doi.org/10.1109/DCIS53048.2021.9666193

Pechmann, S. *et al.* (2021). A Versatile, Voltage-Pulse Based Read and Programming Circuit for Multi-Level RRAM Cells. *Electronics* **2021**, *10*, 530. <u>https://doi.org/10.3390/electronics10050530</u>

Pechmann, S. *et al.* (2021). A Low-Power RRAM Memory Block for Embedded, Multi-Level Weight and Bias Storage in Artificial Neural Networks. *Micromachines* **2021**, *12*, 1277. <u>https://doi.org/10.3390/mi12111277</u>

•••

\_\_\_\_\_

## Thank you for your attention!

Emilio Perez-Bosch Quesada

IHP – Leibniz-Institut für innovative Mikroelektronik Im Technologiepark 25 D – 15236 Frankfurt (Oder) Phone: +49 (0) 335 5625 369 Fax: +49 (0) 335 5625 681 e-mail: quesada@ihp-microelectronics.com

www.ihp-microelectronics.com