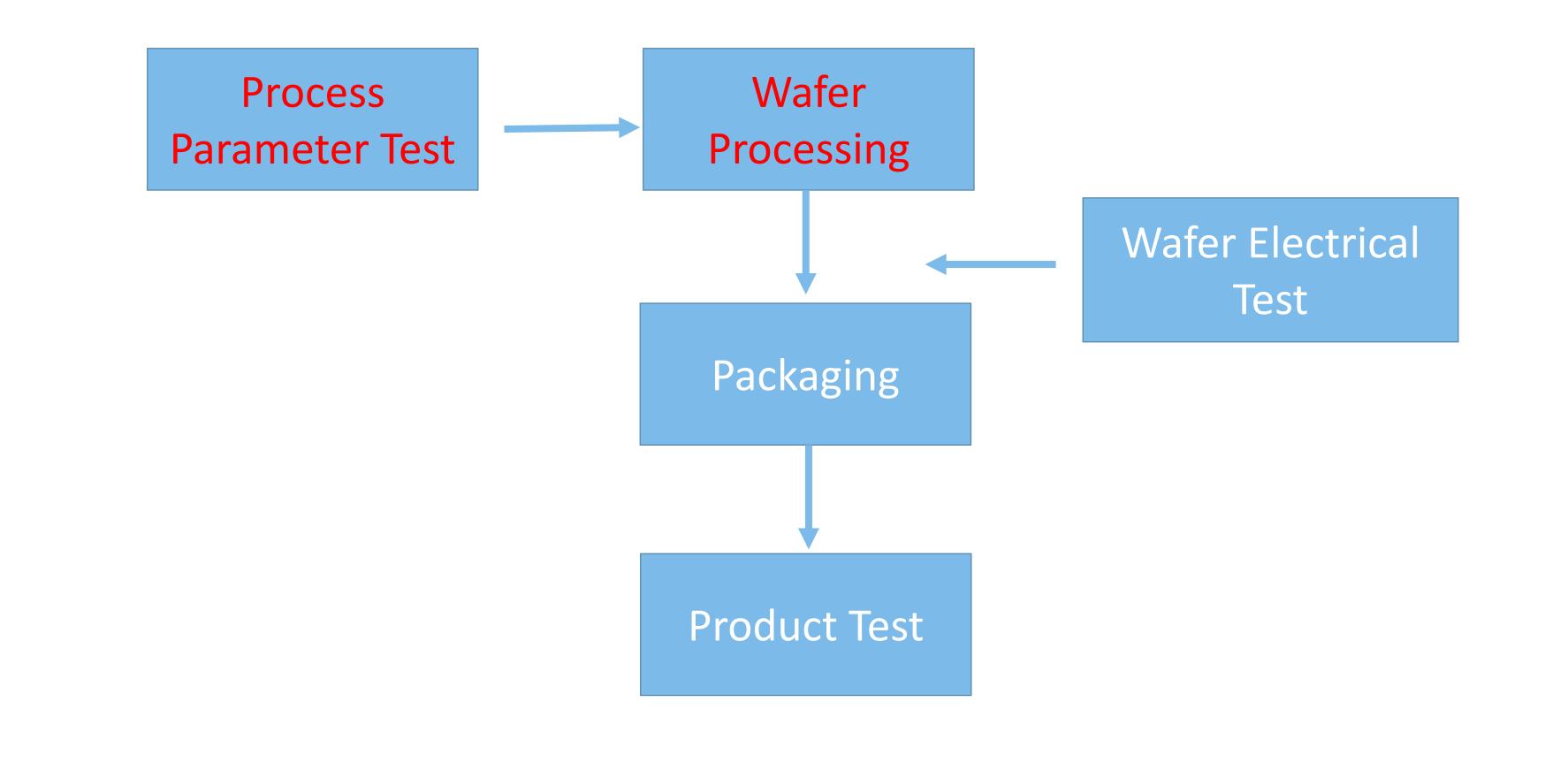

# **RADFET: Wafer to Finished Product**

### <u>Russell Duane</u>, Alan Blake, Mary White, Finbarr Waldron, Anne-Marie Kelleher

innovations for high performance micro<del>c</del>lectronics

UNIVERSIDAD DE GRANADA

# SAND to RADFET

Silicon

**Tyndall Fabrication Facility**

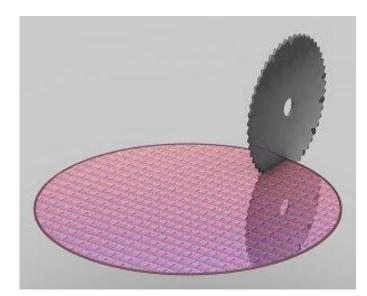

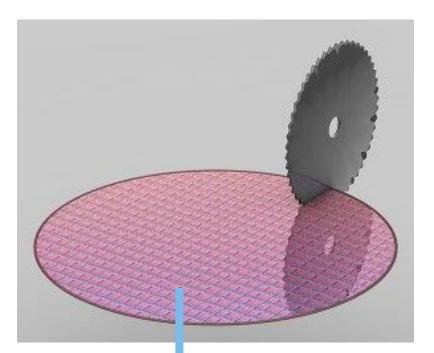

Wafer Dicing into die

Purified into ingot

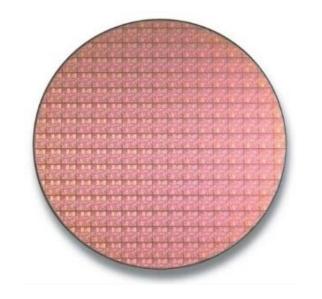

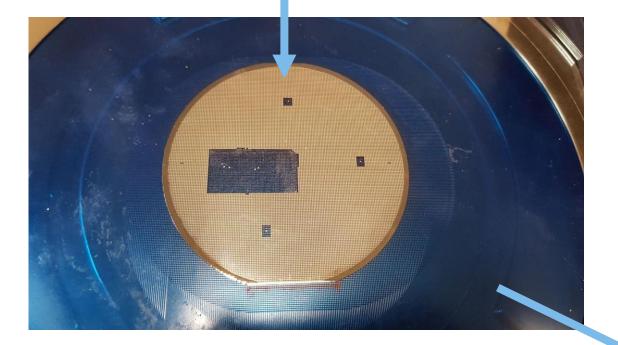

Completed wafer with many RADFET die

Wire Bonding

2<sup>nd</sup> ELICSIR School April 21<sup>st</sup> to 22<sup>nd</sup> 2021

Ingot sawn into 100mm wafers

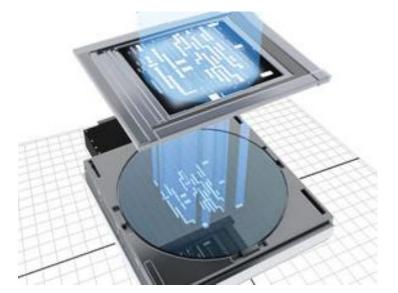

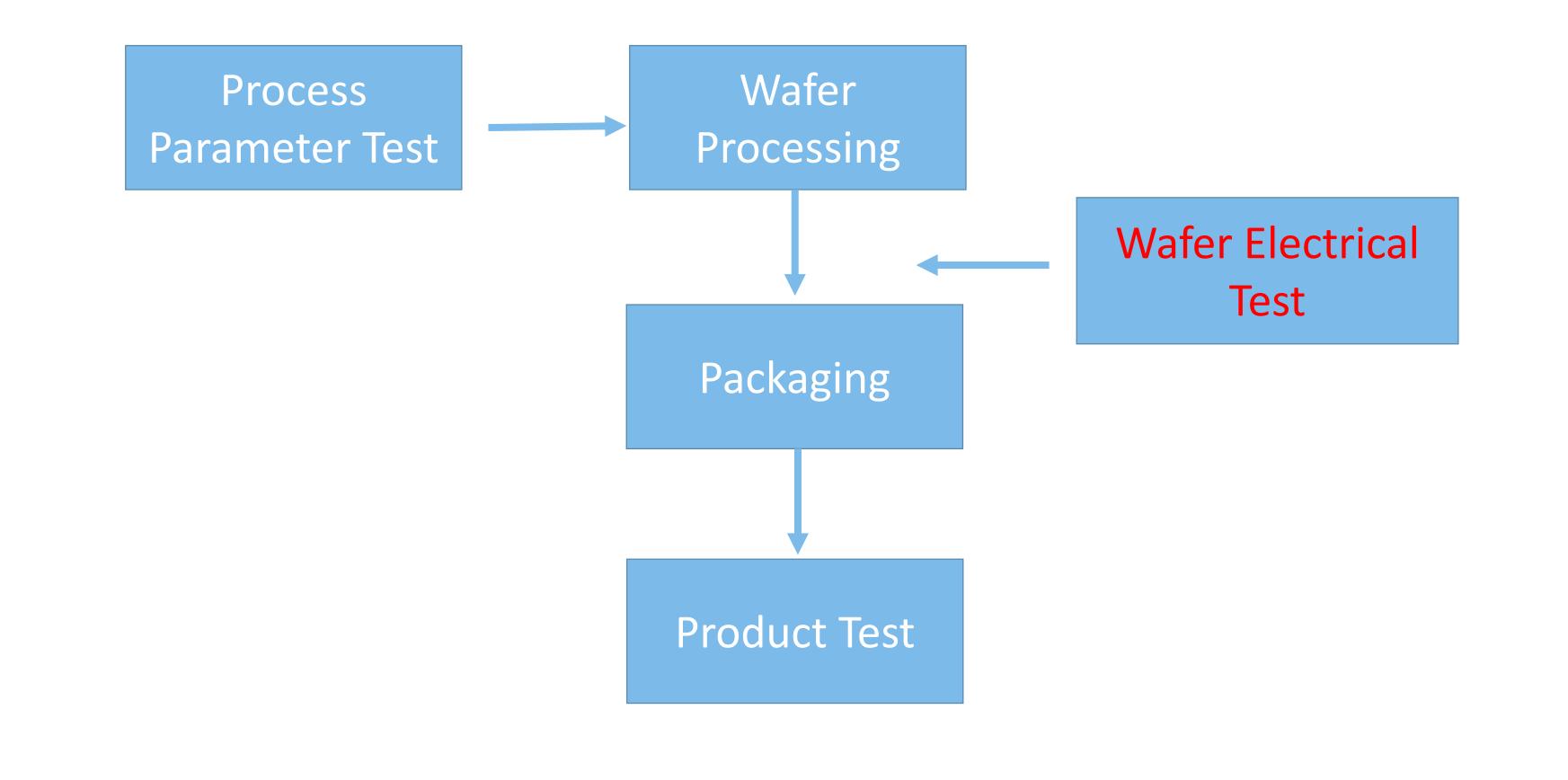

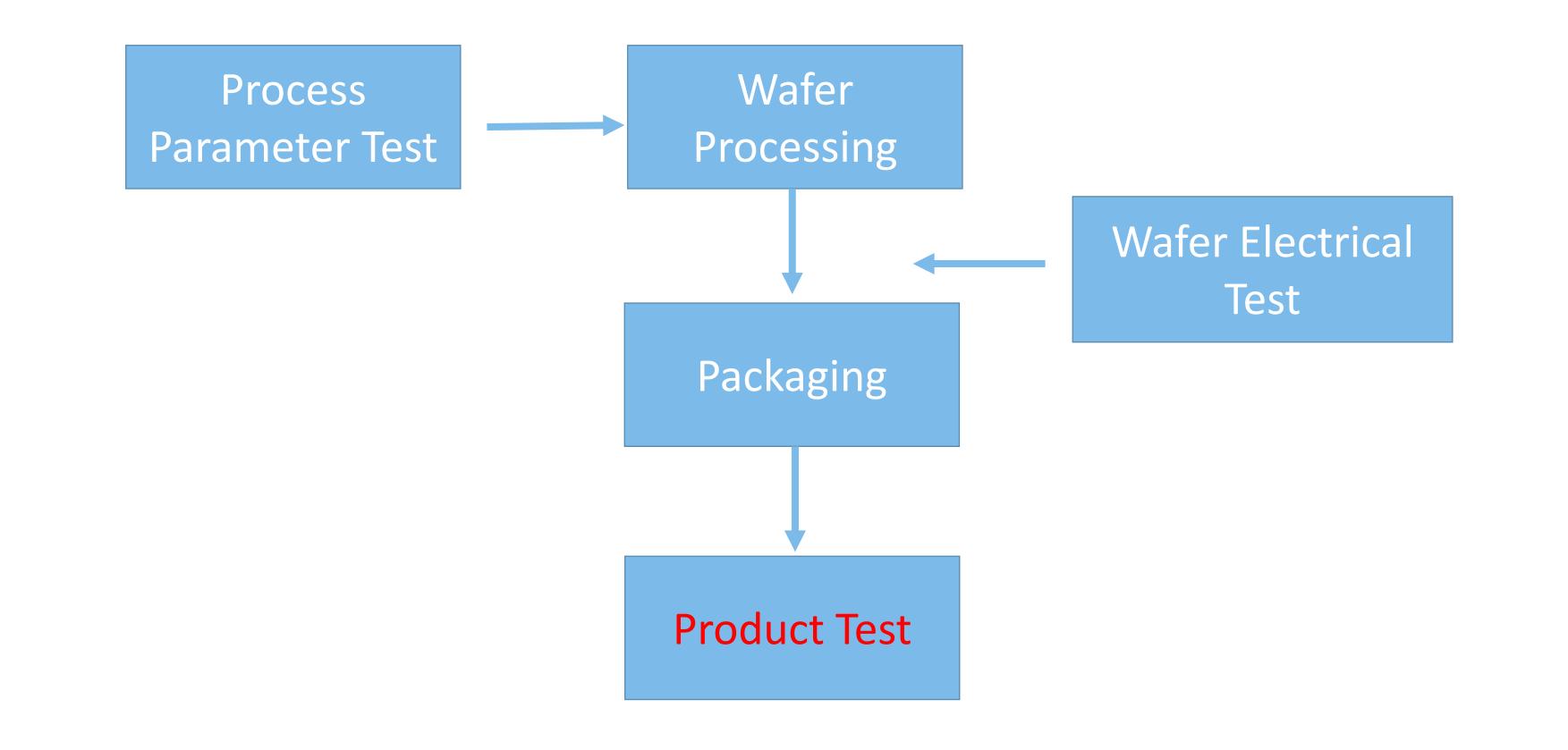

#### Wafer Electrical Testing

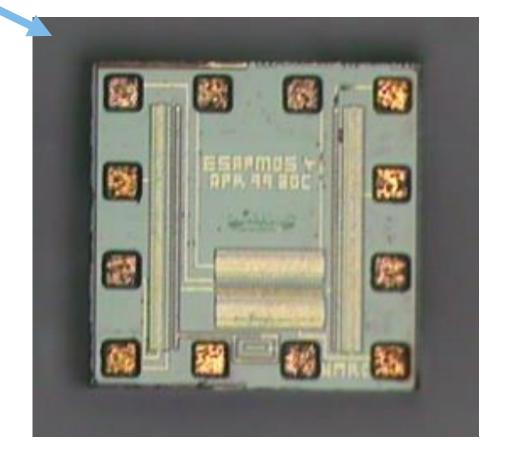

Packaged RADFET

Product Test

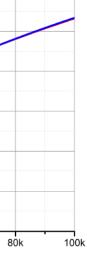

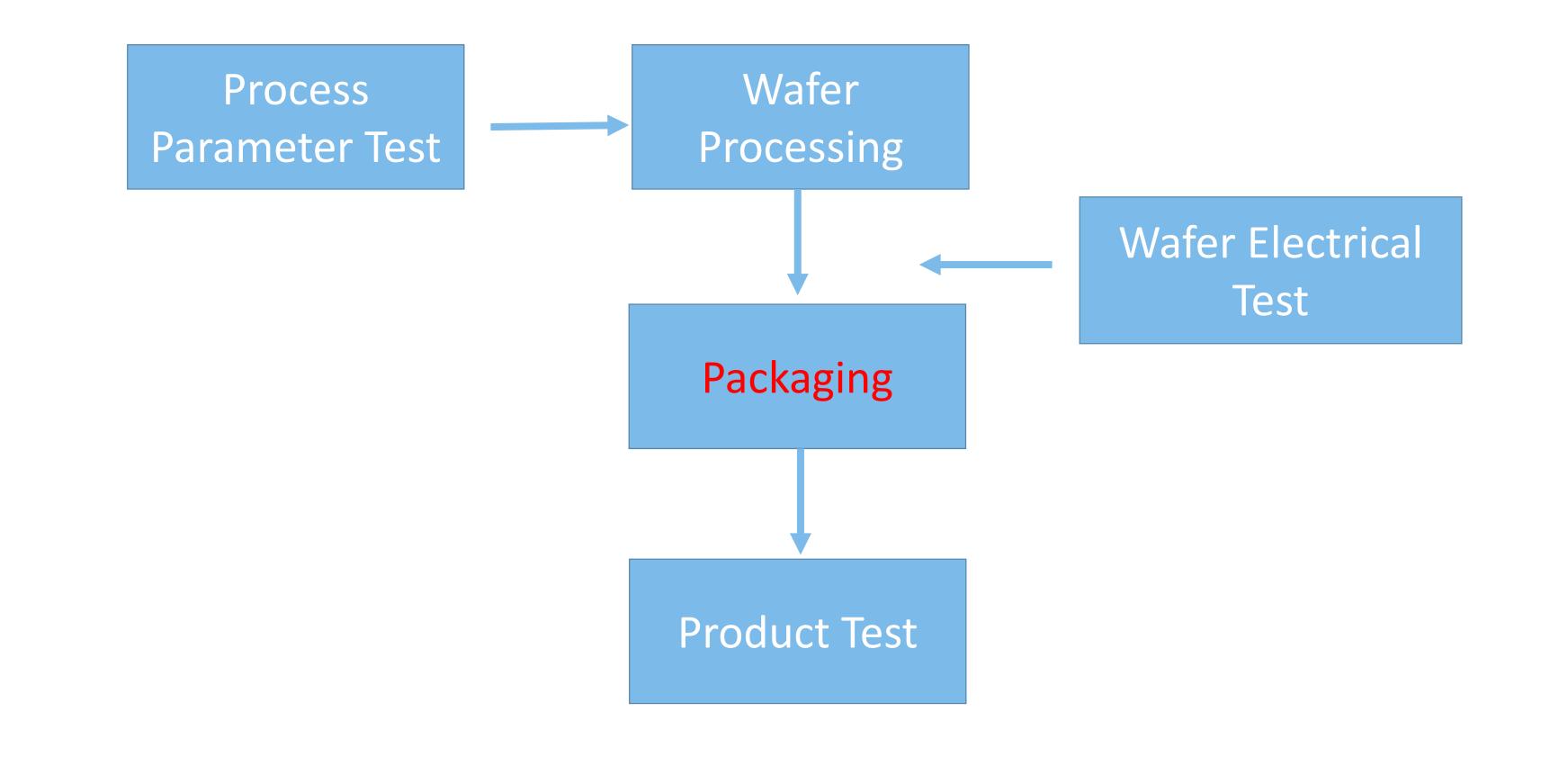

### **Detector Fabrication**

2<sup>nd</sup> ELICSIR School April 21<sup>st</sup> to 22<sup>nd</sup> 2021

## Outline

2<sup>nd</sup> ELICSIR School April 21<sup>st</sup> to 22<sup>nd</sup> 2021

# **Tyndall Fabrication Facilities**

- Wafer diameters from 50mm to 200mm

- Range of fabrication clean-rooms for different applications

- Class 1000 (ISO 6) or lower

#### ISO 14644-1 Cleanroom Standards

|       | www.portafab.com/cleanrooms.html |                      |                      |            |           |         |               |  |

|-------|----------------------------------|----------------------|----------------------|------------|-----------|---------|---------------|--|

| Class | maximum particles/m <sup>3</sup> |                      |                      |            |           |         | FED STD 209E  |  |

|       | ≥0.1 µm                          | ≥0.2 µm              | ≥0.3 µm              | ≥0.5 µm    | ≥1 µm     | ≥5 µm   | equivalent    |  |

| ISO 1 | 10                               | 2.37                 | 1.02                 | 0.35       | 0.083     | 0.0029  |               |  |

| ISO 2 | 100                              | 23.7                 | 10.2                 | 3.5        | 0.83      | 0.029   |               |  |

| ISO 3 | 1,000                            | 237                  | 102                  | 35         | 8.3       | 0.29    | Class 1       |  |

| ISO 4 | 10,000                           | 2,370                | 1,020                | 352        | 83        | 2.9     | Class 10      |  |

| ISO 5 | 100,000                          | 23,700               | 10,200               | 3,520      | 832       | 29      | Class 100     |  |

| 150.6 | 1.0×10 <sup>6</sup>              | 237,000              | 102,000              | 35,200     | 8,320     | 293     | Class 1,000   |  |

| ISO 7 | 1.0×10 <sup>7</sup>              | 2.37×10 <sup>6</sup> | 1,020,000            | 352,000    | 83,200    | 2,930   | Class 10,000  |  |

| ISO 8 | 1.0×10 <sup>8</sup>              | 2.37×10 <sup>7</sup> | 1.02×10 <sup>7</sup> | 3,520,000  | 832,000   | 29,300  | Class 100,000 |  |

| ISO 9 | 1.0×10 <sup>9</sup>              | 2.37×10 <sup>8</sup> | 1.02×10 <sup>8</sup> | 35,200,000 | 8,320,000 | 293,000 | Room air      |  |

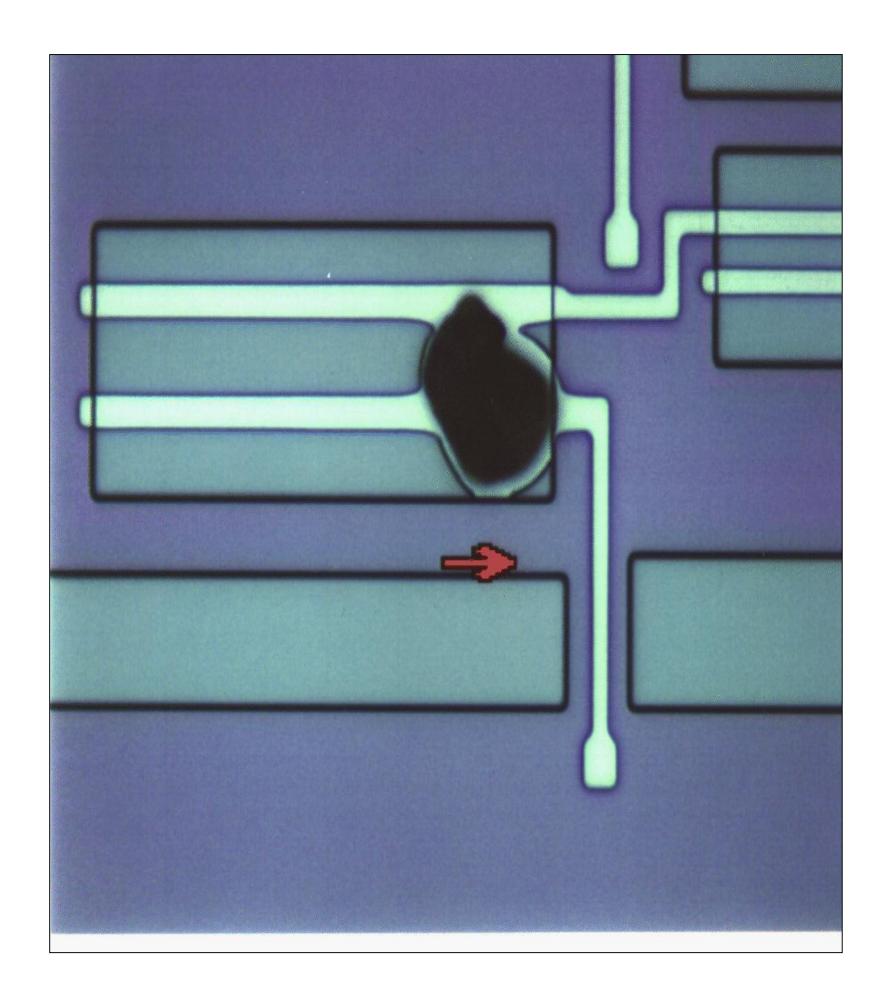

# Cleanliness important

### Particle causing a Metal Short

### 2<sup>nd</sup> ELICSIR School April 21<sup>st</sup> to 22<sup>nd</sup> 2021

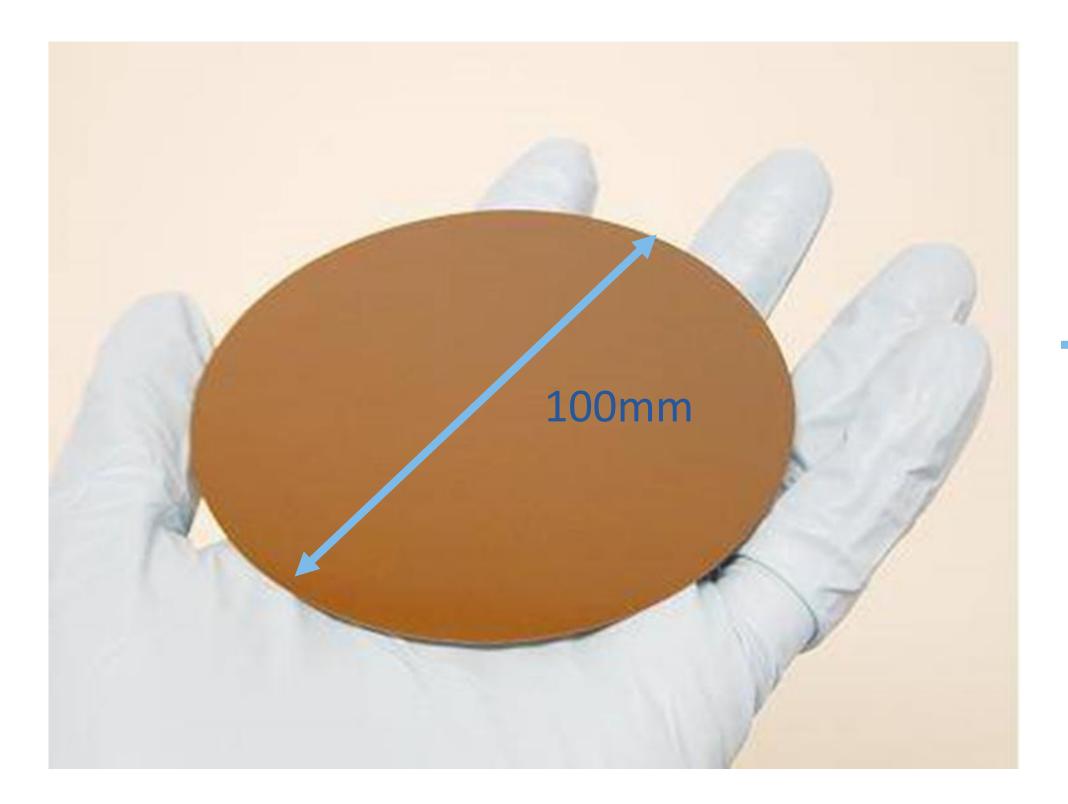

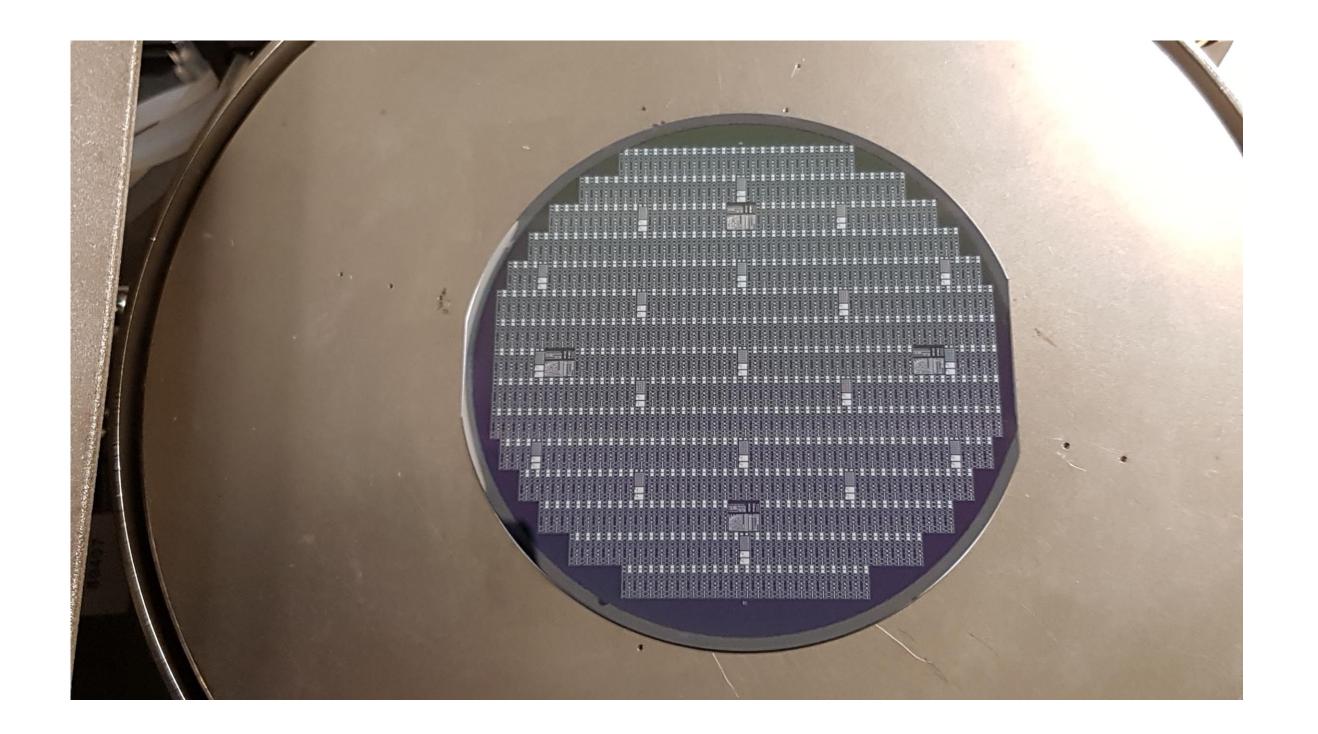

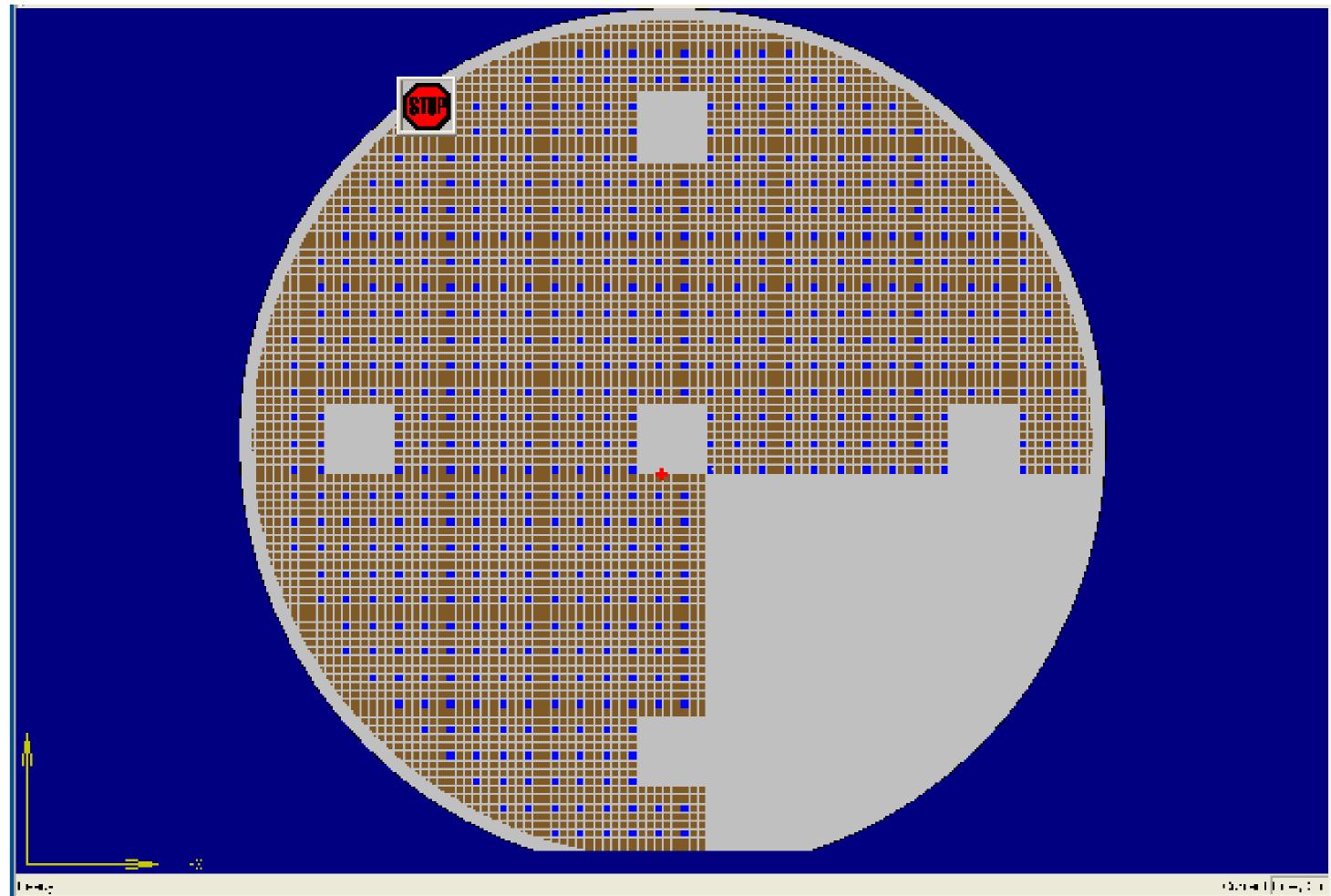

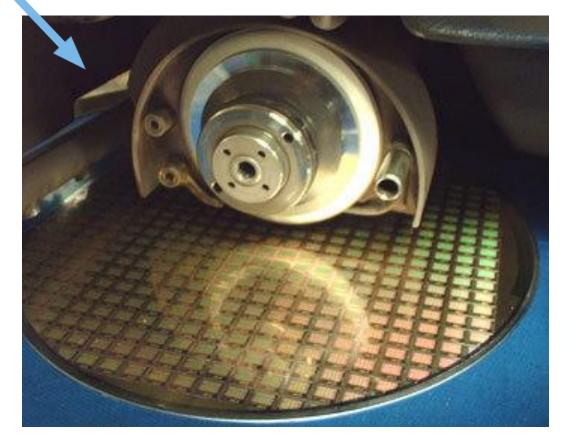

# 100mm RADFET Wafer

2<sup>nd</sup> ELICSIR School April 21<sup>st</sup> to 22<sup>nd</sup> 2021

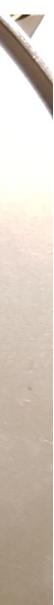

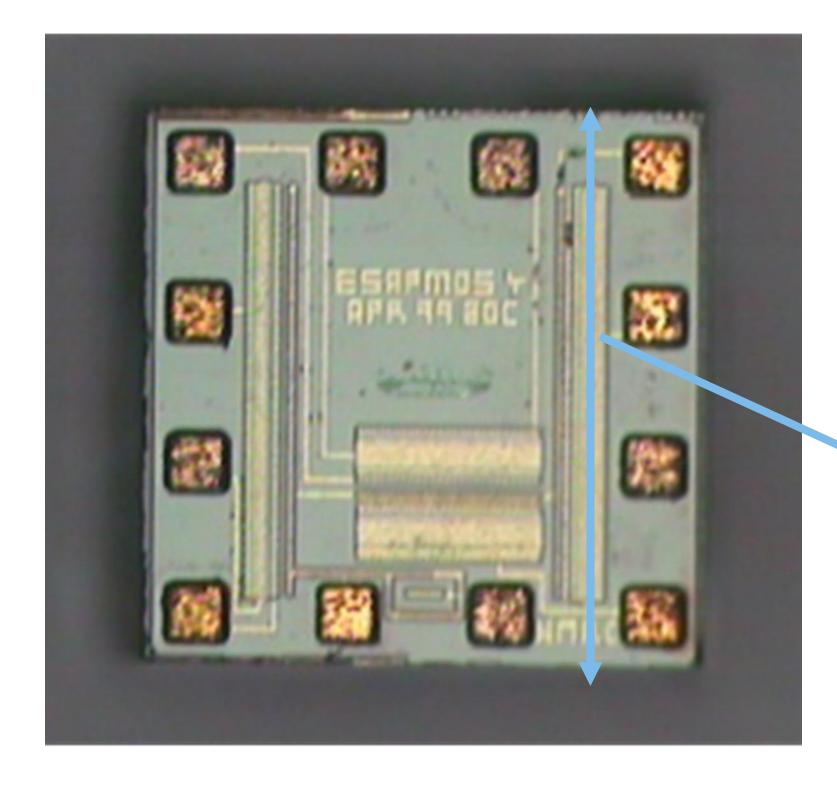

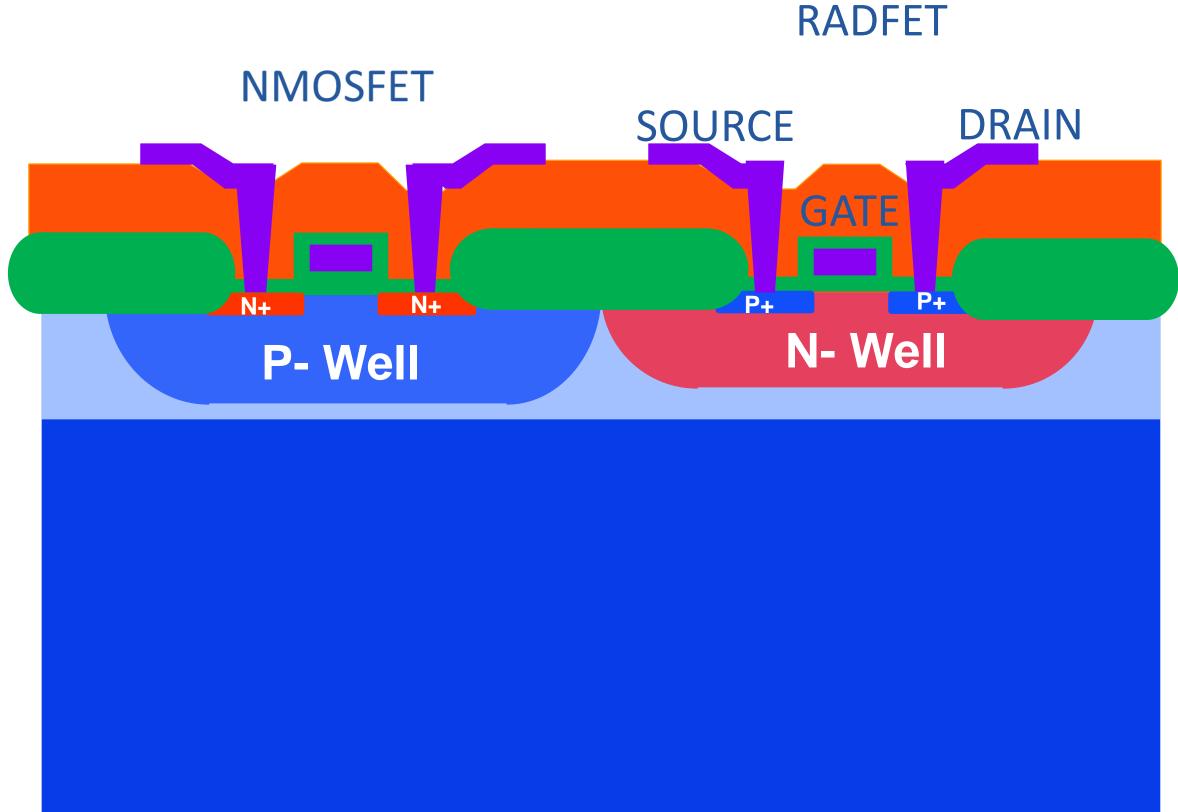

# **RADFET transistor Cross-Section**

#### 1mm

1mm

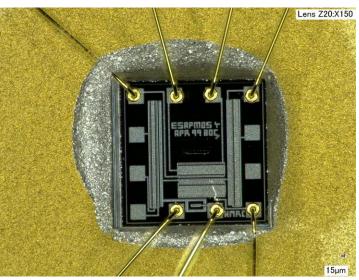

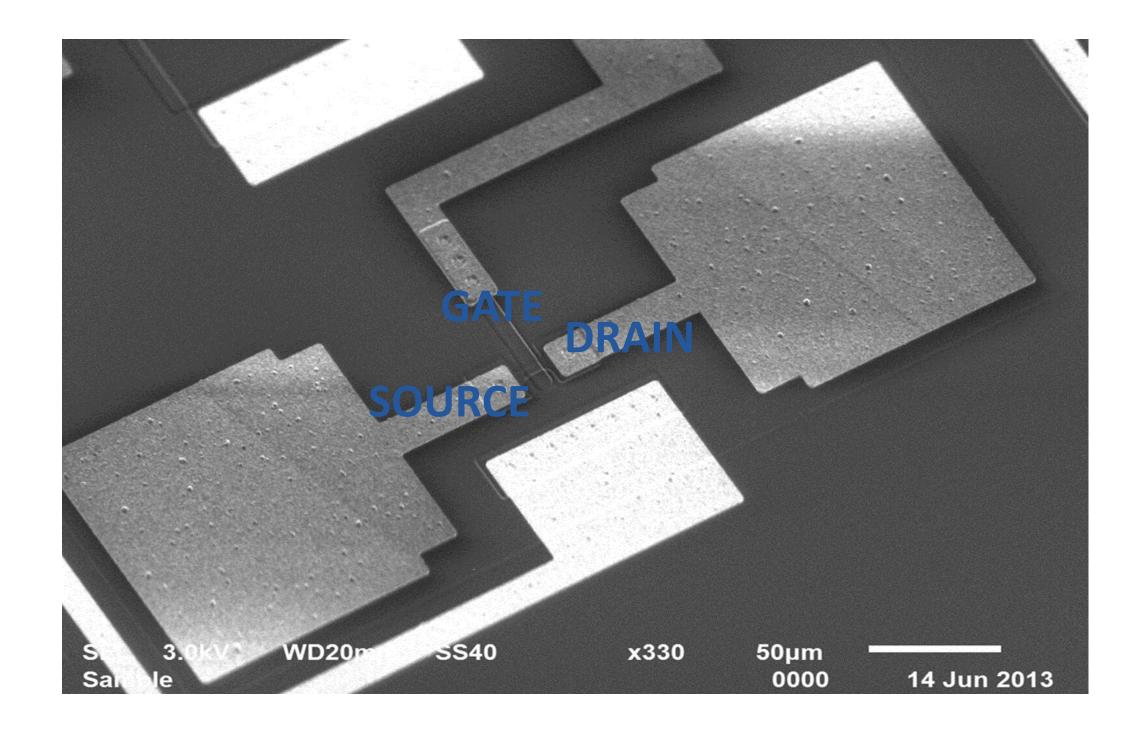

### RADFET Die Design

#### 2<sup>nd</sup> ELICSIR School April 21<sup>st</sup> to 22<sup>nd</sup> 2021

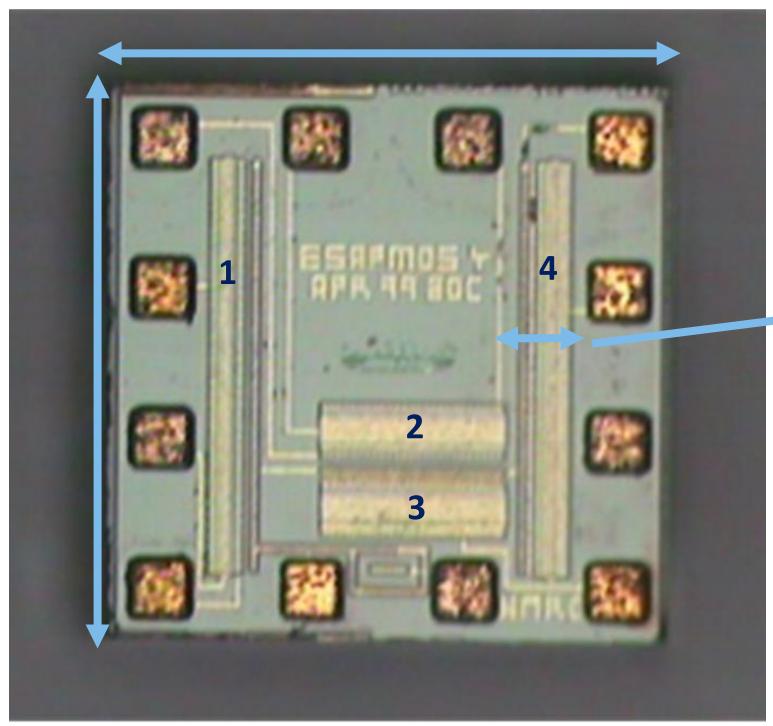

#### **RADFET Manufacture**

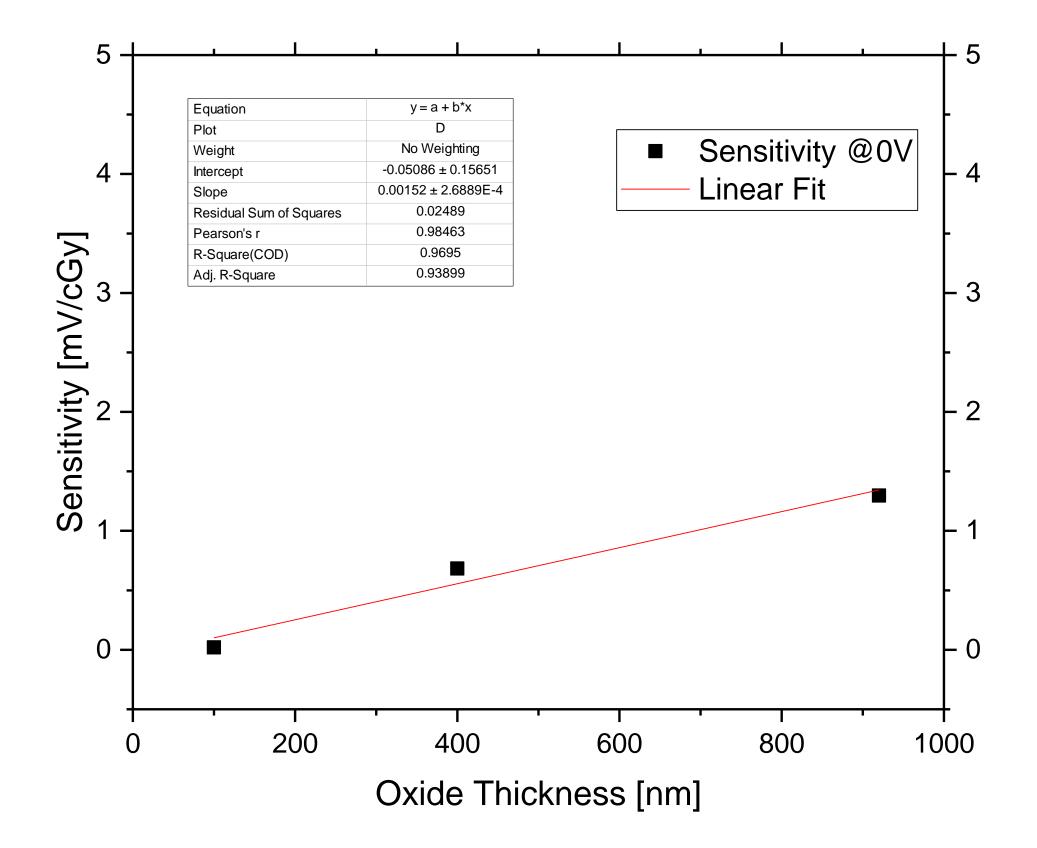

Sensitivity:  $\Delta V_{\text{threshold}} = Q_{\text{oxide}}/C_{\text{sensor}}$

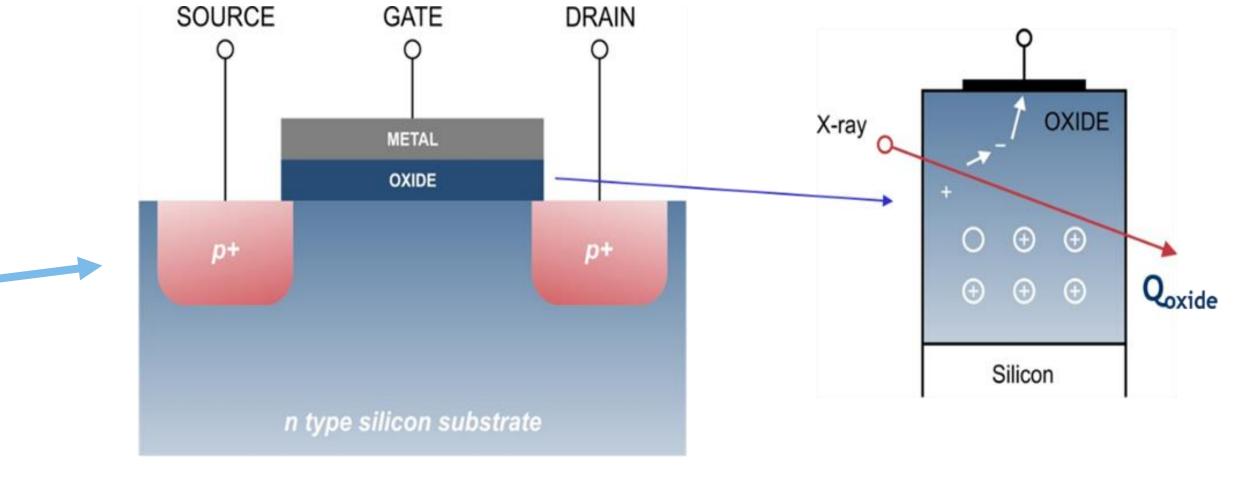

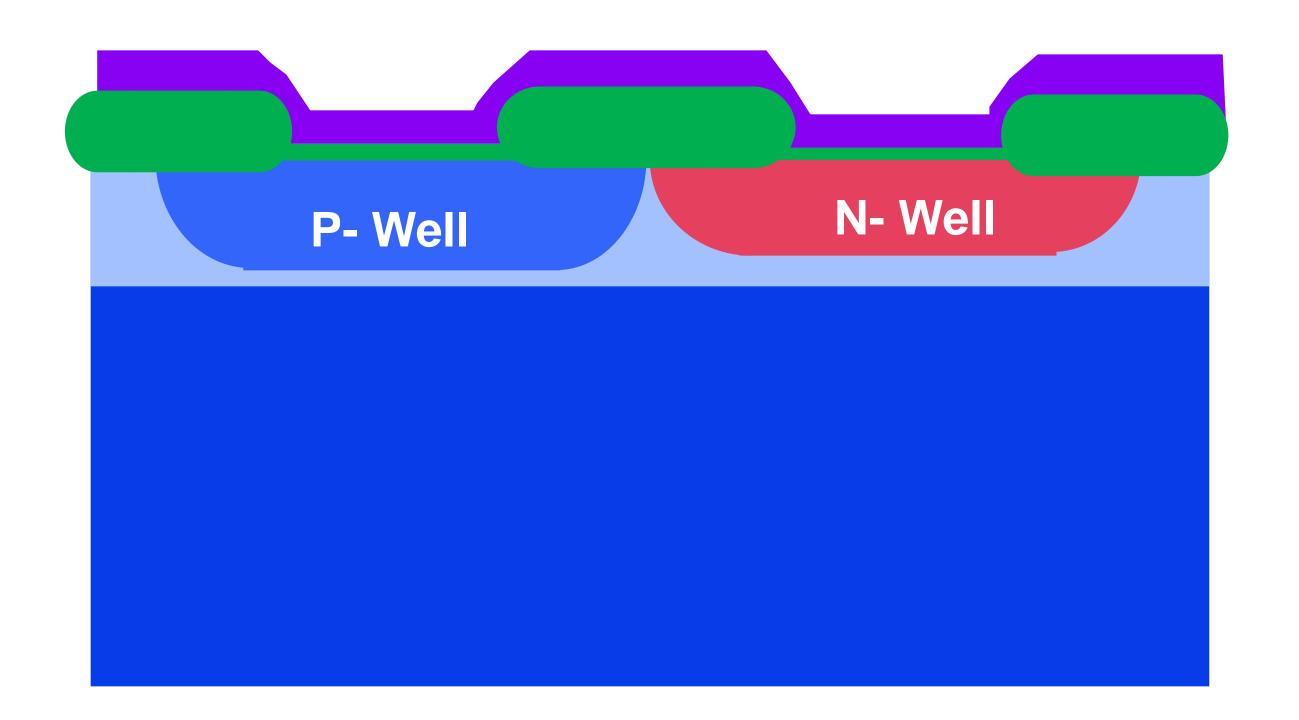

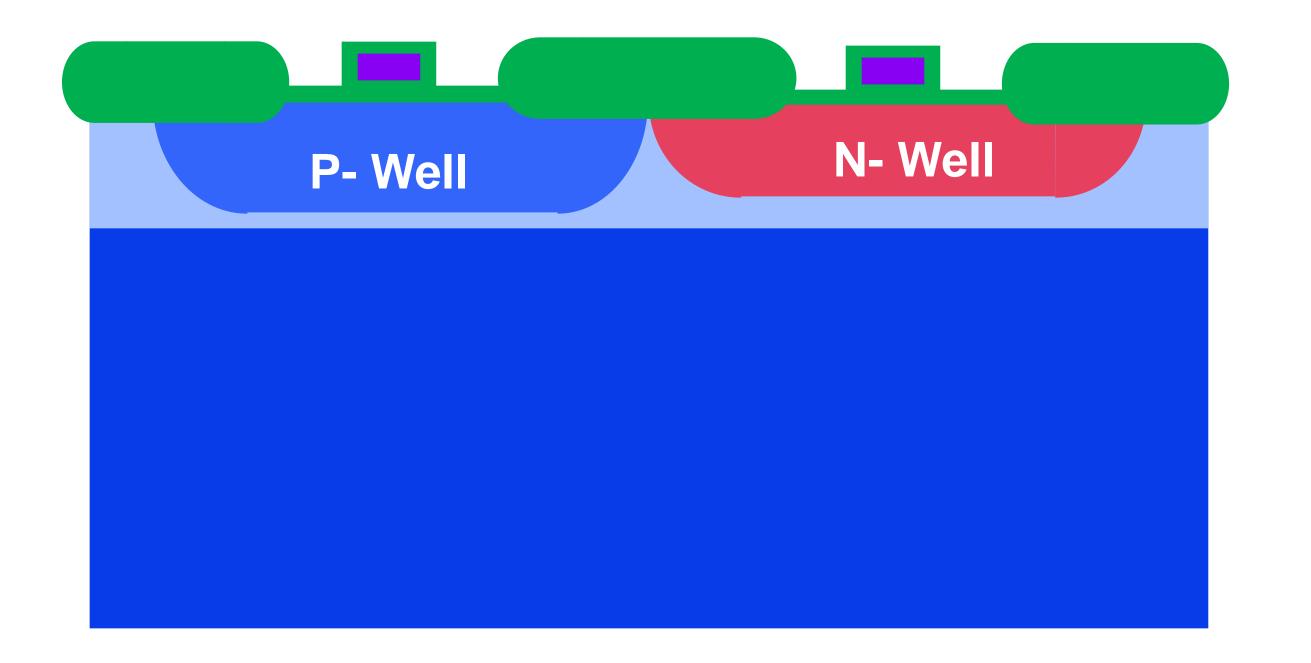

## **CMOS transistor Cross-Section**

2<sup>nd</sup> ELICSIR School April 21<sup>st</sup> to 22<sup>nd</sup> 2021

- Integrate RADFET in our CMOS line

- More than 100 process steps

# Silicon Wafer

P- Epitaxy layer

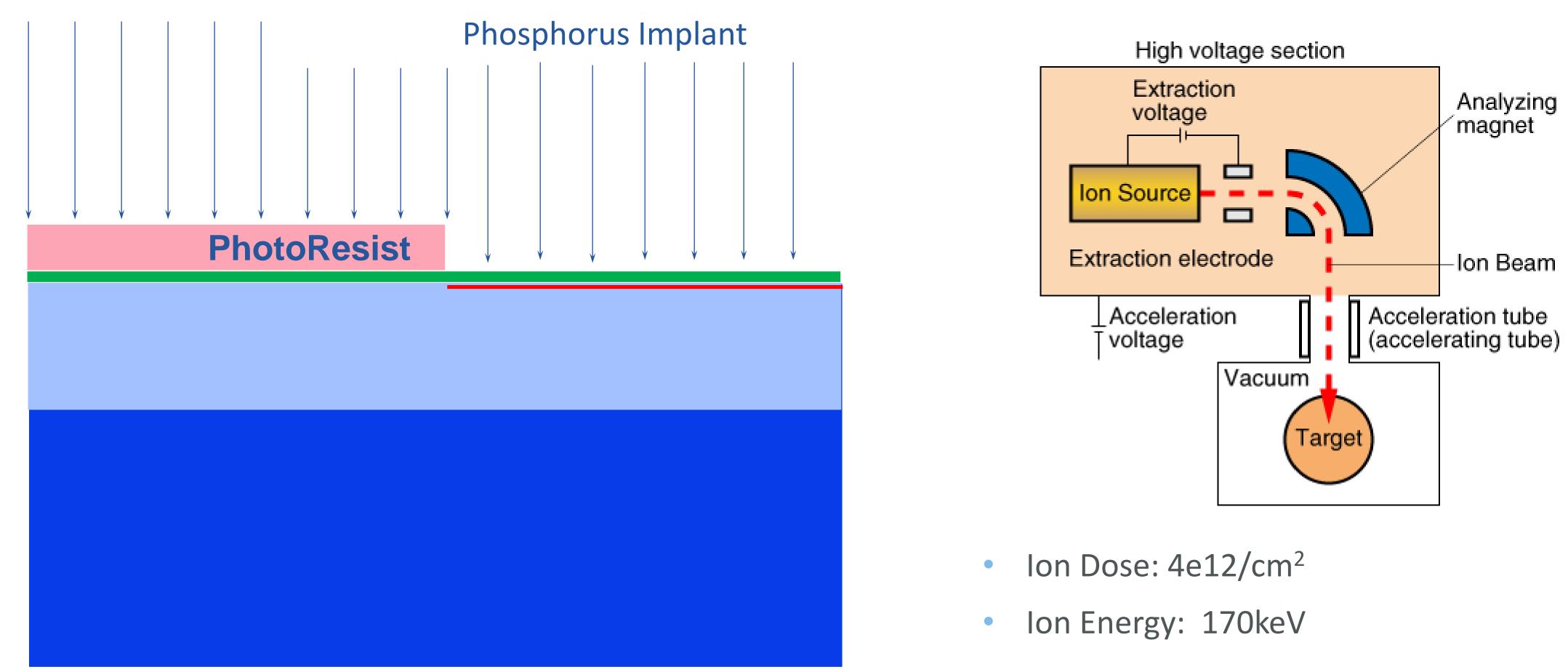

# NWell Mask and Implant

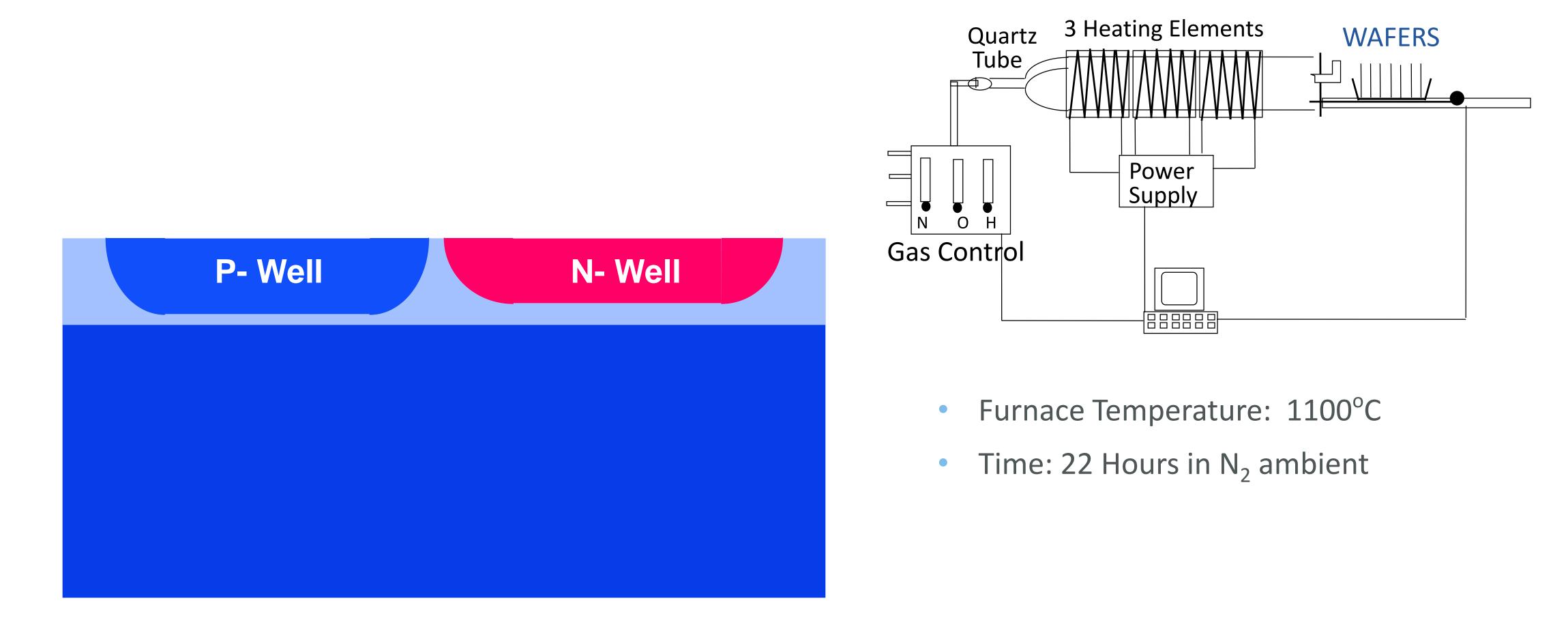

# Well Drive-in

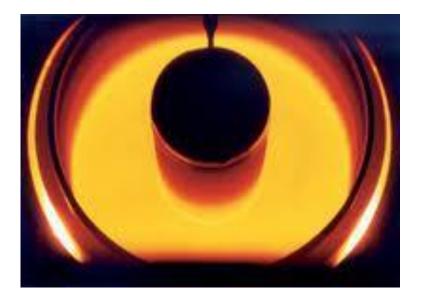

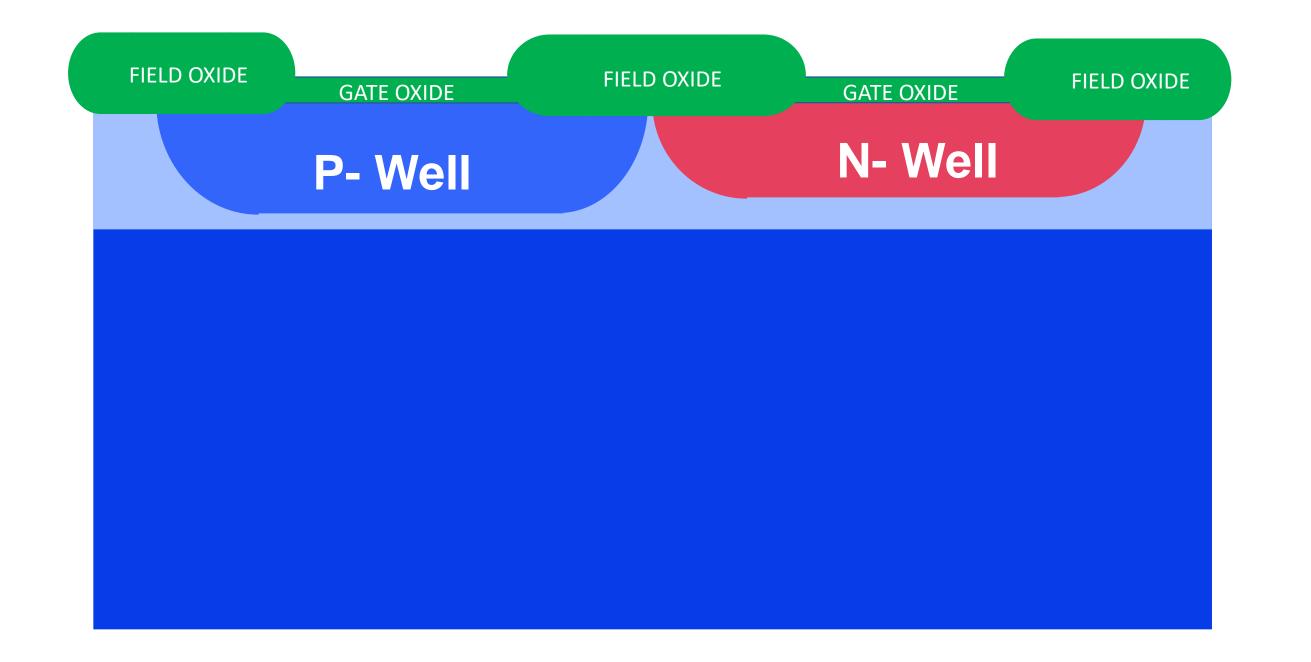

# Gate Oxidation

- 100nm, 400nm, 1µm thicknesses

- Grown in Furnace at high temperatures in an oxygen environment

$Si + O_2 = SiO_2$

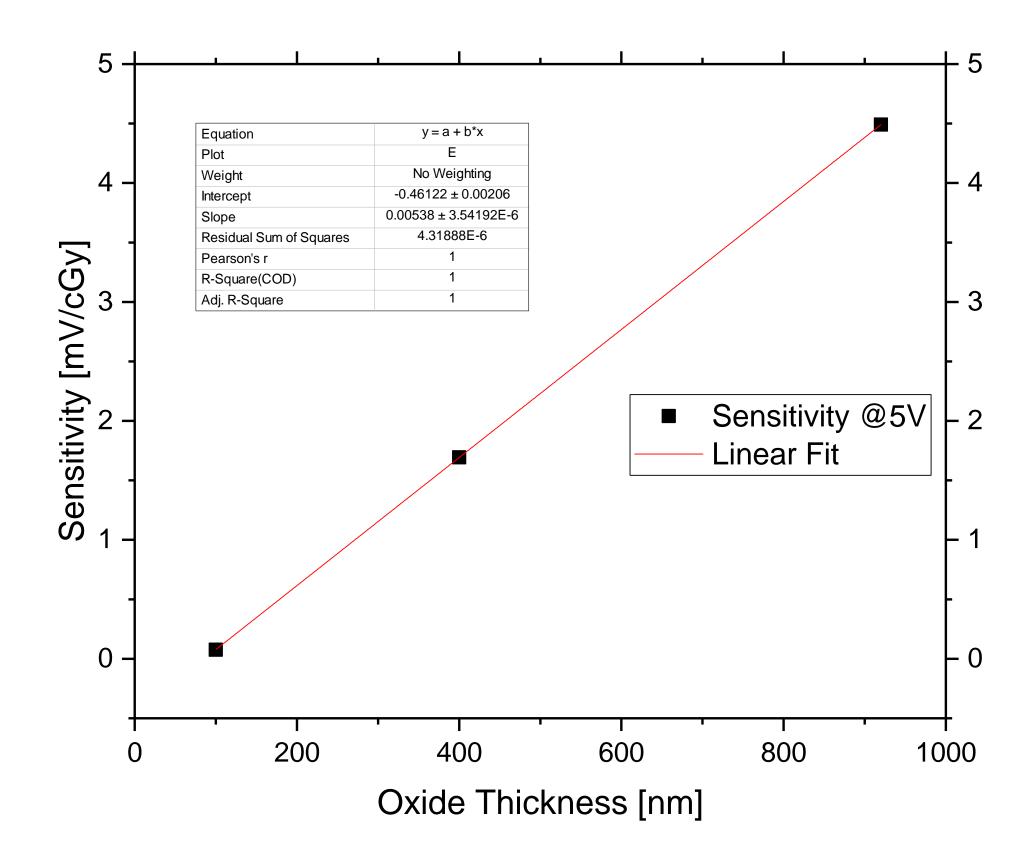

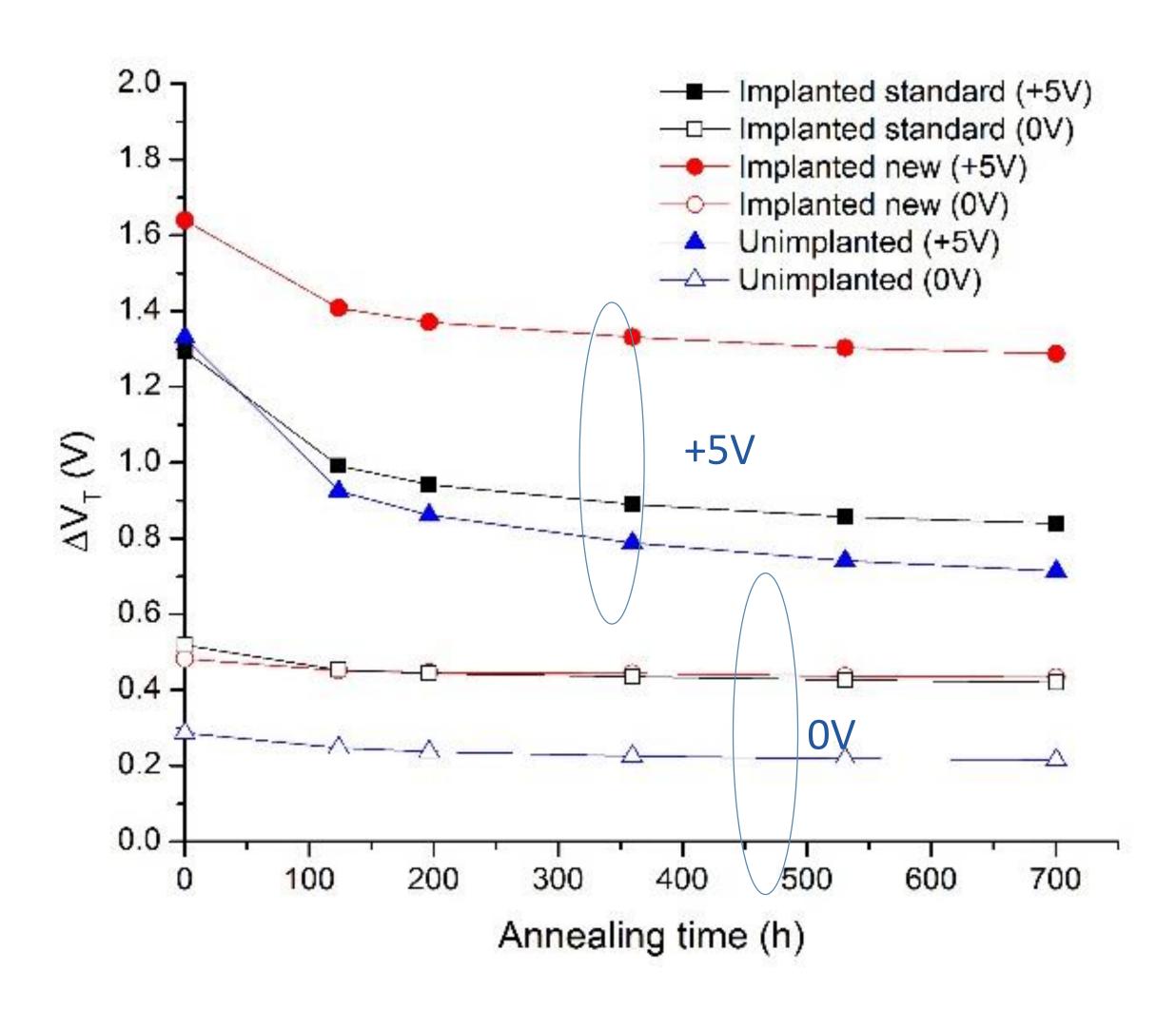

# Sensitivity vs Oxide Thickness

**RADFET Manufacture**

### Measurement of Gate Oxide

### NanoSpec Optical Measurement Tool

2<sup>nd</sup> ELICSIR School April 21<sup>st</sup> to 22<sup>nd</sup> 2021

| Design               | 400nm       |  |  |

|----------------------|-------------|--|--|

| Specification        | 400 ± 20 nm |  |  |

| Measured (13 points) | 394 ± 5 nm  |  |  |

# **Polysilicon Gate Deposition**

2<sup>nd</sup> ELICSIR School April 21<sup>st</sup> to 22<sup>nd</sup> 2021

- **Chemical Vapour Deposition**

- 450nm Polysilicon

- Temperature: 620°C

- Time: 50min

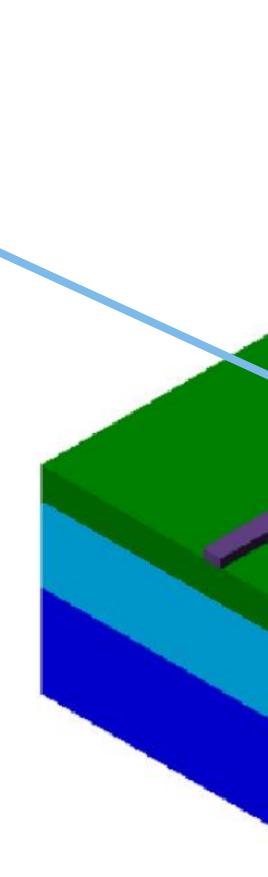

# Etch Polysilicon Gate

2<sup>nd</sup> ELICSIR School April 21<sup>st</sup> to 22<sup>nd</sup> 2021

- Photoresist is deposited and patterned

- Etch the polysilicon

- Strip the resist

### 3-D View

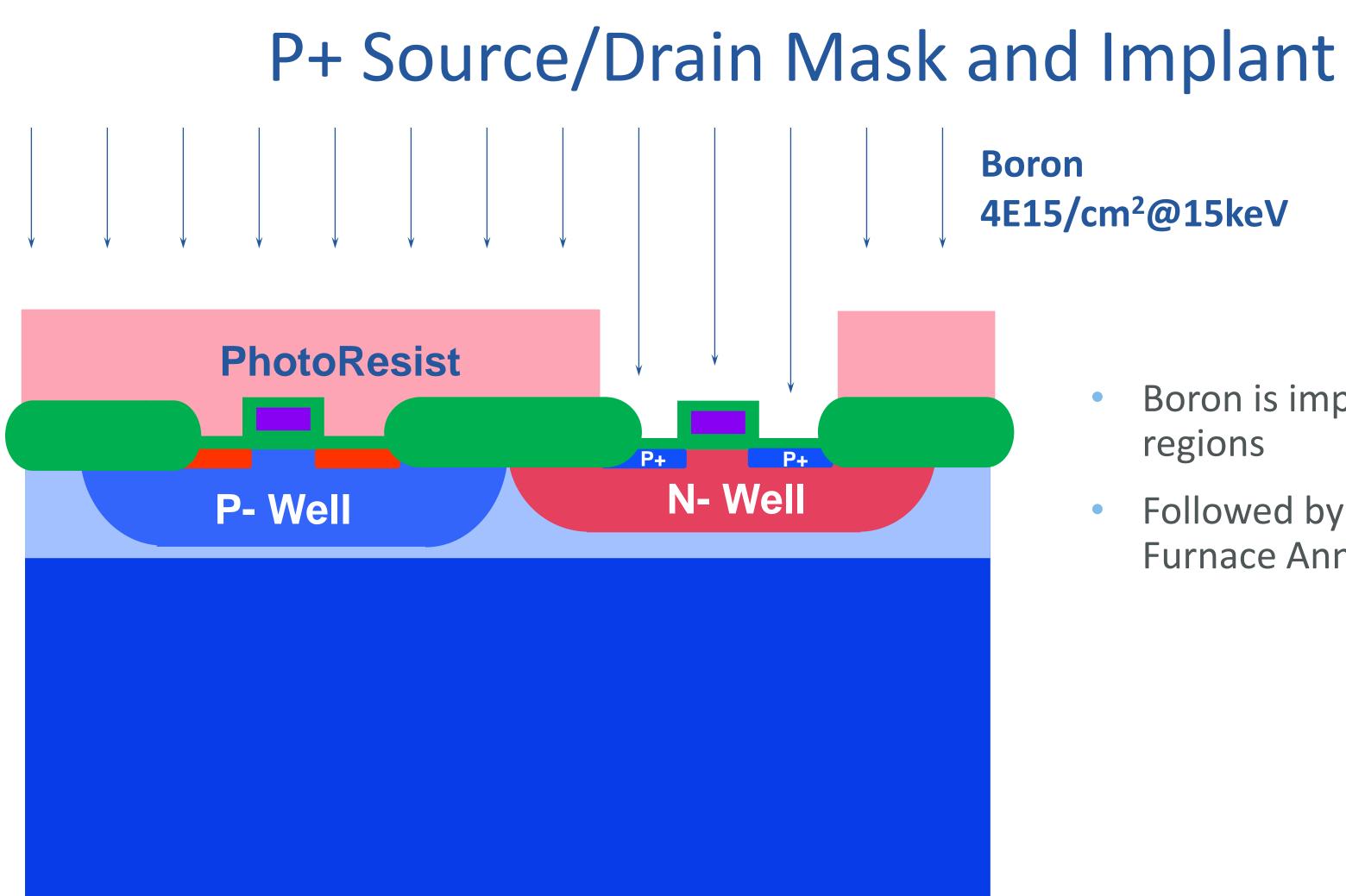

## Poly Oxidation

2<sup>nd</sup> ELICSIR School April 21<sup>st</sup> to 22<sup>nd</sup> 2021

- Temperature: 900°C

- Time: 105min O<sub>2</sub>

2<sup>nd</sup> ELICSIR School April 21<sup>st</sup> to 22<sup>nd</sup> 2021

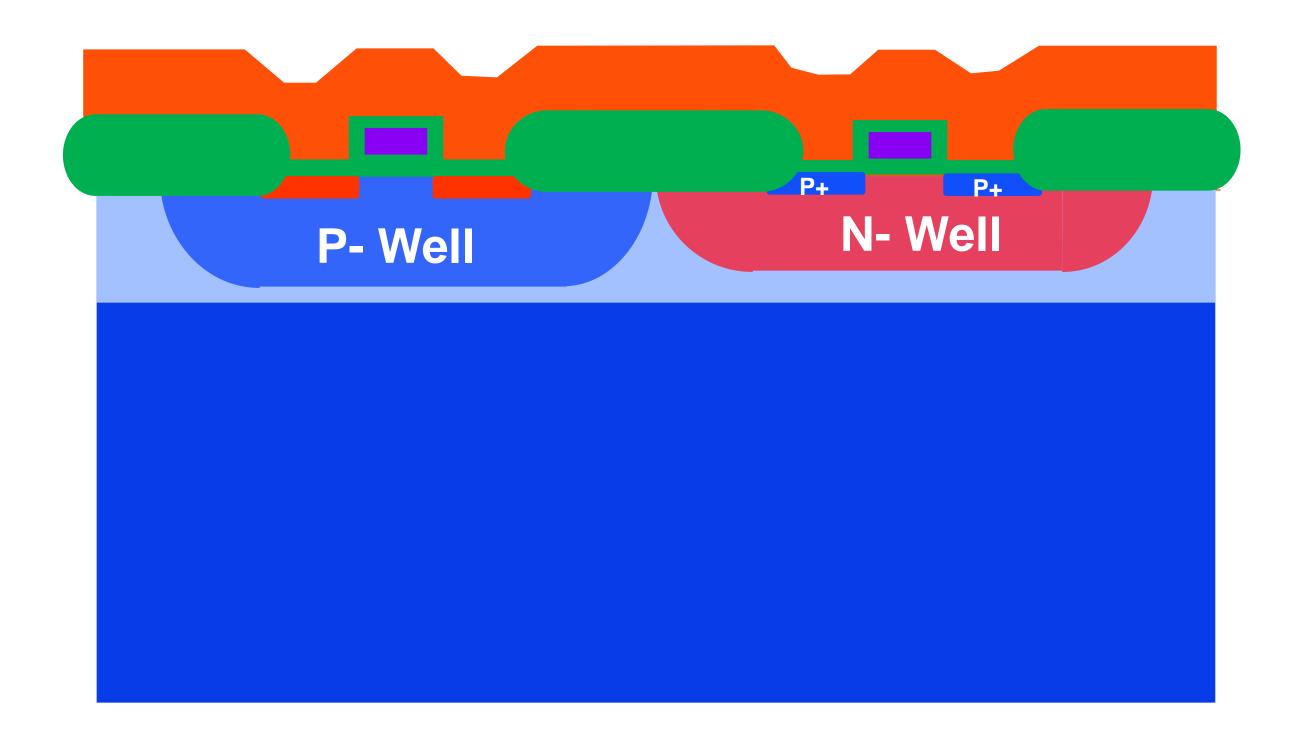

Boron 4E15/cm<sup>2</sup>@15keV

- Boron is implanted into the P+ S/D regions

- Followed by High Temperature **Furnace Anneal**

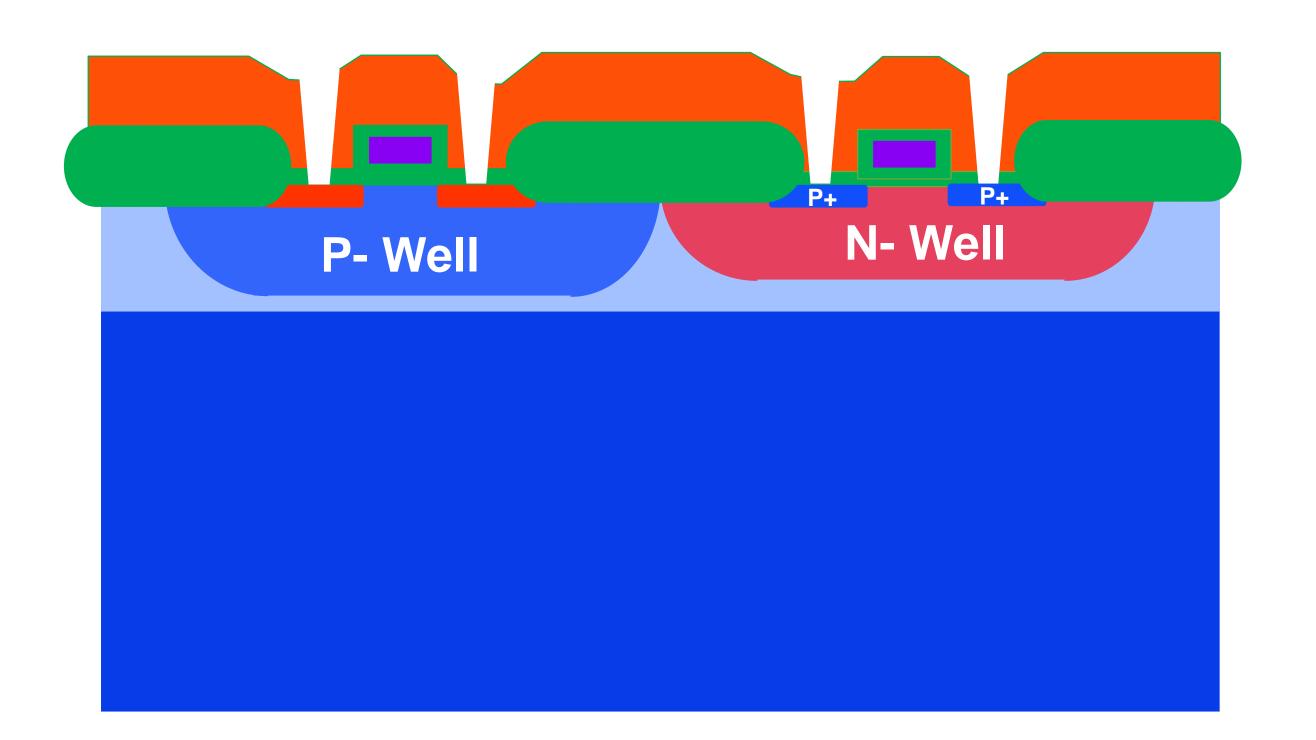

# Deposit Dielectric

2<sup>nd</sup> ELICSIR School April 21<sup>st</sup> to 22<sup>nd</sup> 2021

Planarise surface prior to metal deposition

### **Contact Holes**

2<sup>nd</sup> ELICSIR School April 21<sup>st</sup> to 22<sup>nd</sup> 2021

Contact holes are etched through to the Source and Drain diffusions and the polysilicon gates

2<sup>nd</sup> ELICSIR School April 21<sup>st</sup> to 22<sup>nd</sup> 2021

- 0.5µm thick Metal

- Aluminium/0.5% Silicon Alloy

- Patterned and then etched to form electrodes

### **Processing Temperature**

### **PMOS Transistor**

### 2<sup>nd</sup> ELICSIR School April 21<sup>st</sup> to 22<sup>nd</sup> 2021

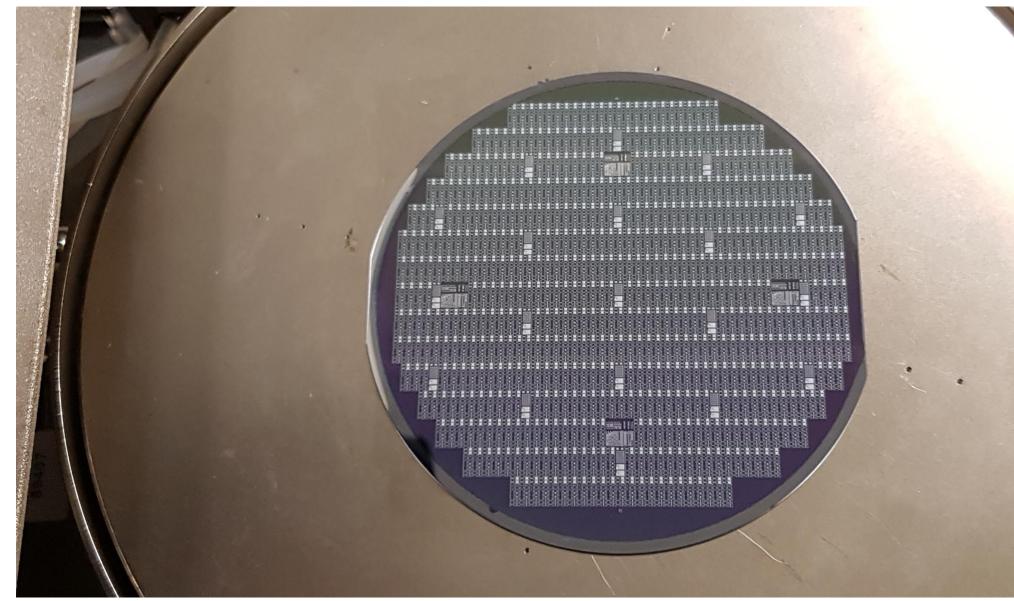

# Finished Wafer

#### 2<sup>nd</sup> ELICSIR School April 21<sup>st</sup> to 22<sup>nd</sup> 2021

## Outline

2<sup>nd</sup> ELICSIR School April 21<sup>st</sup> to 22<sup>nd</sup> 2021

# Wafer Testing

### 2<sup>nd</sup> ELICSIR School April 21<sup>st</sup> to 22<sup>nd</sup> 2021

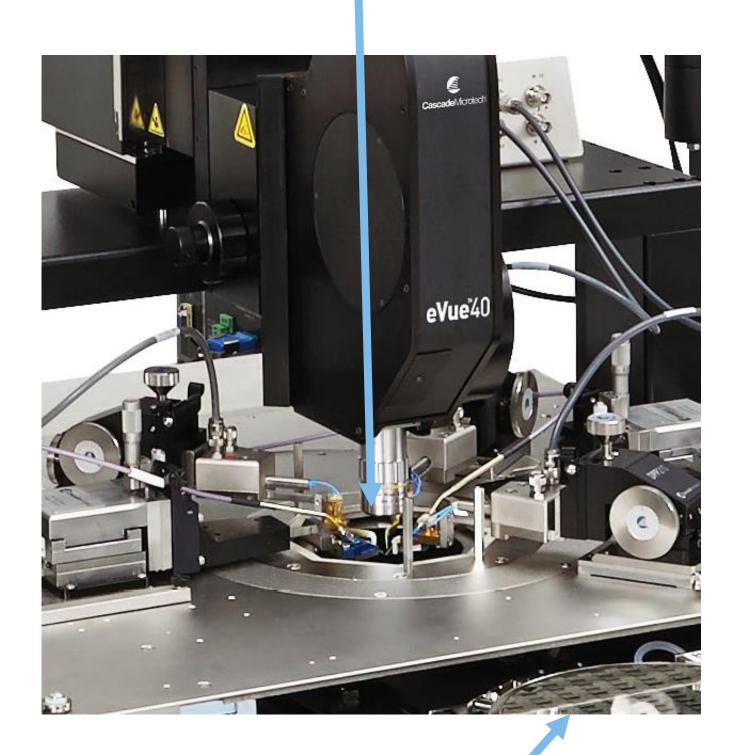

### **Cascade Semi-automatic Probe Station**

### Probe Needles positioned above Microchamber

### Wafer Loading into MicroChamber

2<sup>nd</sup> ELICSIR School April 21<sup>st</sup> to 22<sup>nd</sup> 2021

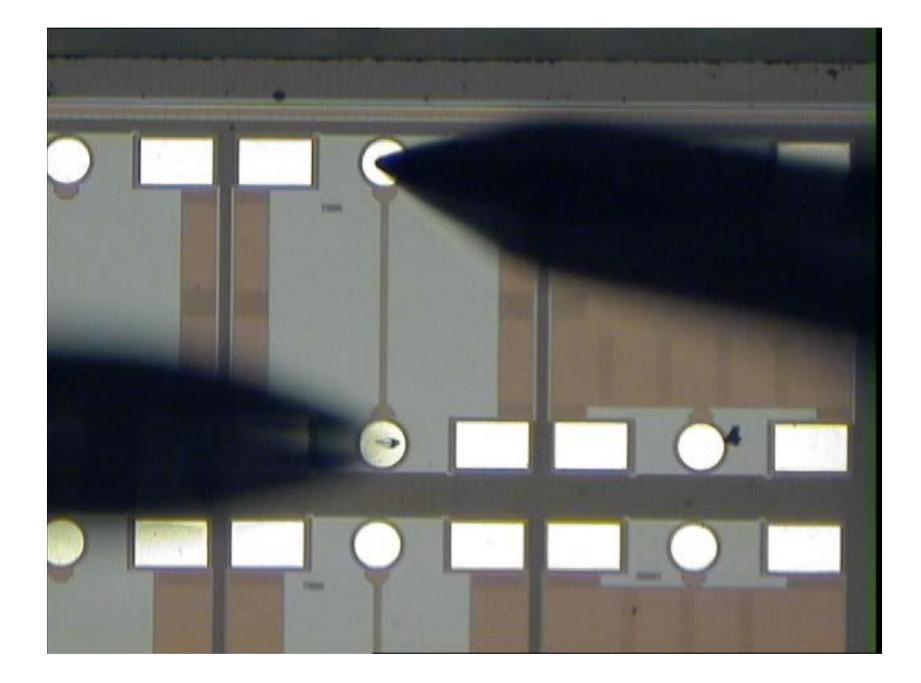

Tungsten Probe Needles touching 100um\*100um Metal Pads

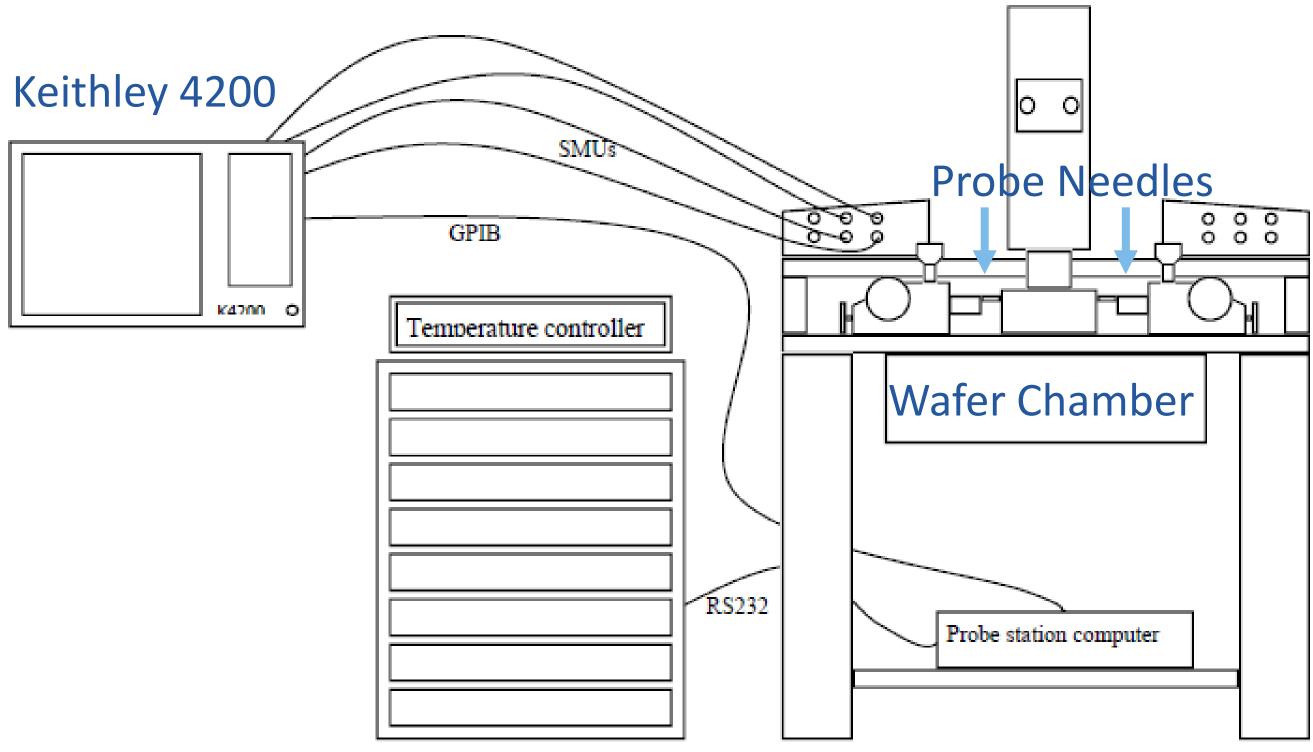

## Measurement System

- Keithley 4200 Parameter Analyzer

- **Electrical Source-Measure Units** (SMU)

- Keithley 4200 controls probe station

- Wafer movement

- Wafer Temperature

**Probe Station**

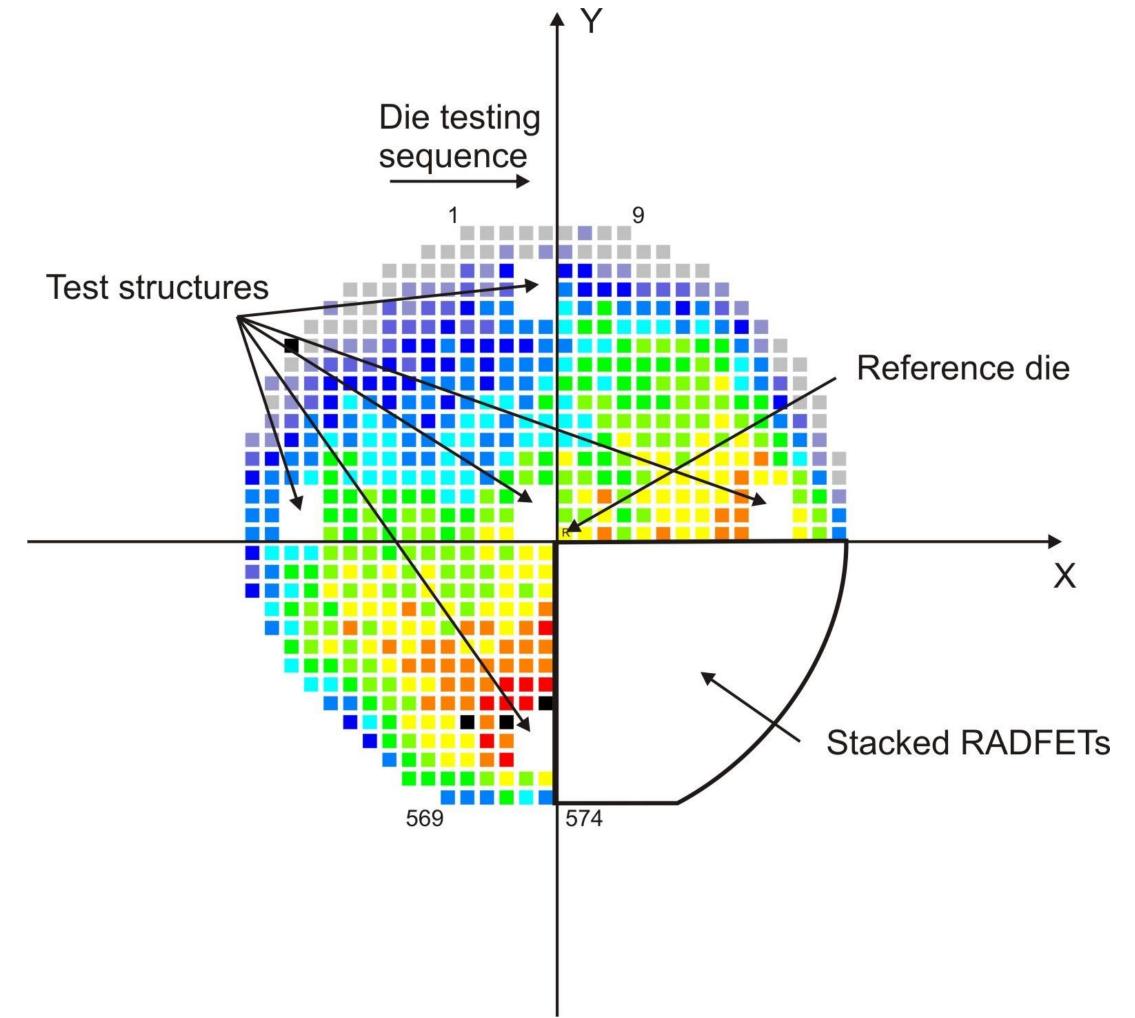

# Typical Wafer Map

~200 chips tested out of >4,000/wafer

2<sup>nd</sup> ELICSIR School April 21<sup>st</sup> to 22<sup>nd</sup> 2021

**RADFET Manufacture**

Tyndall National Institu Institiúid Náisiúnta

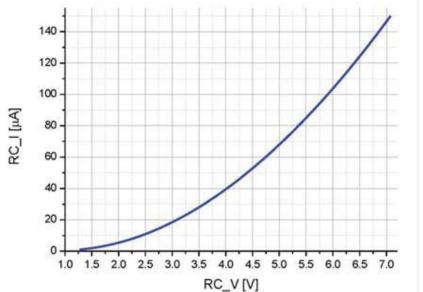

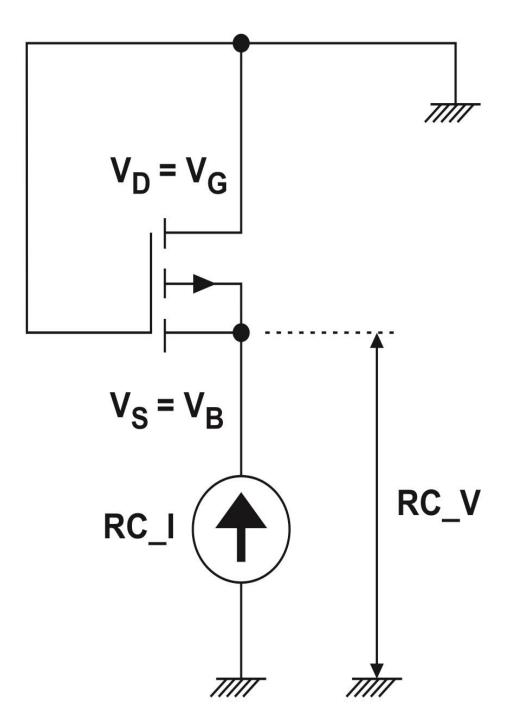

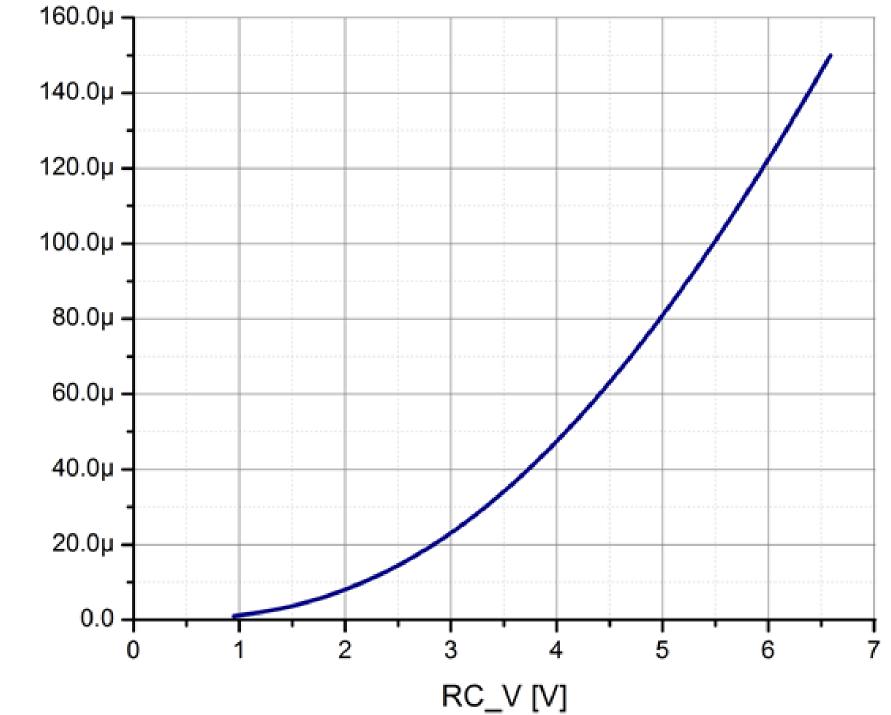

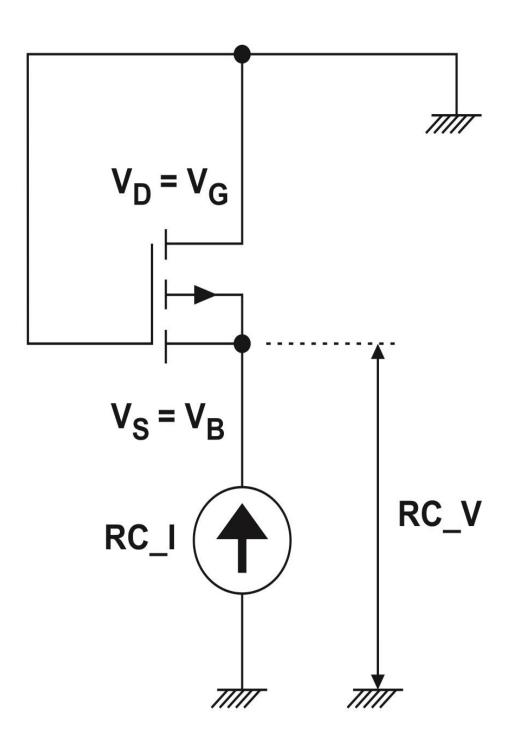

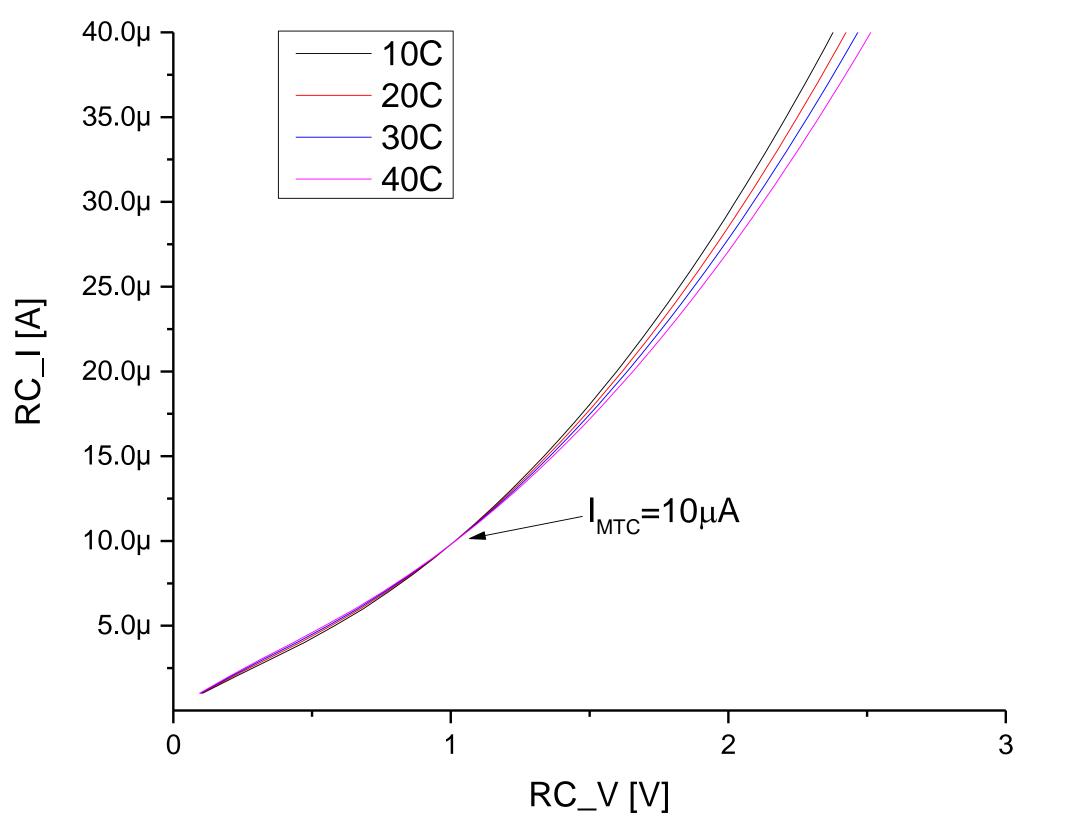

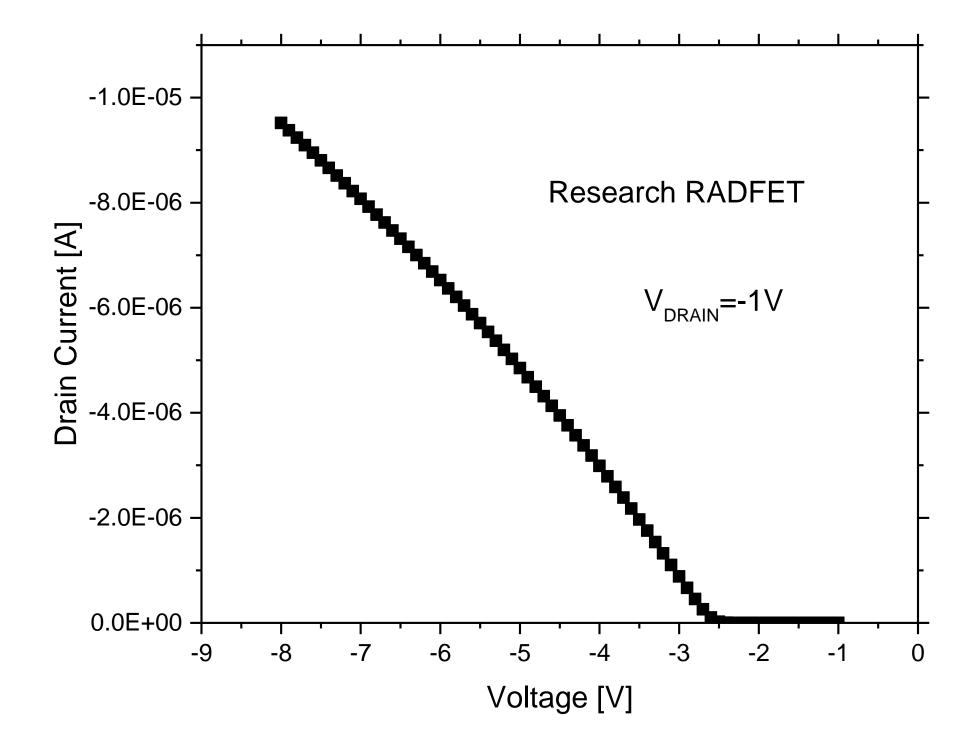

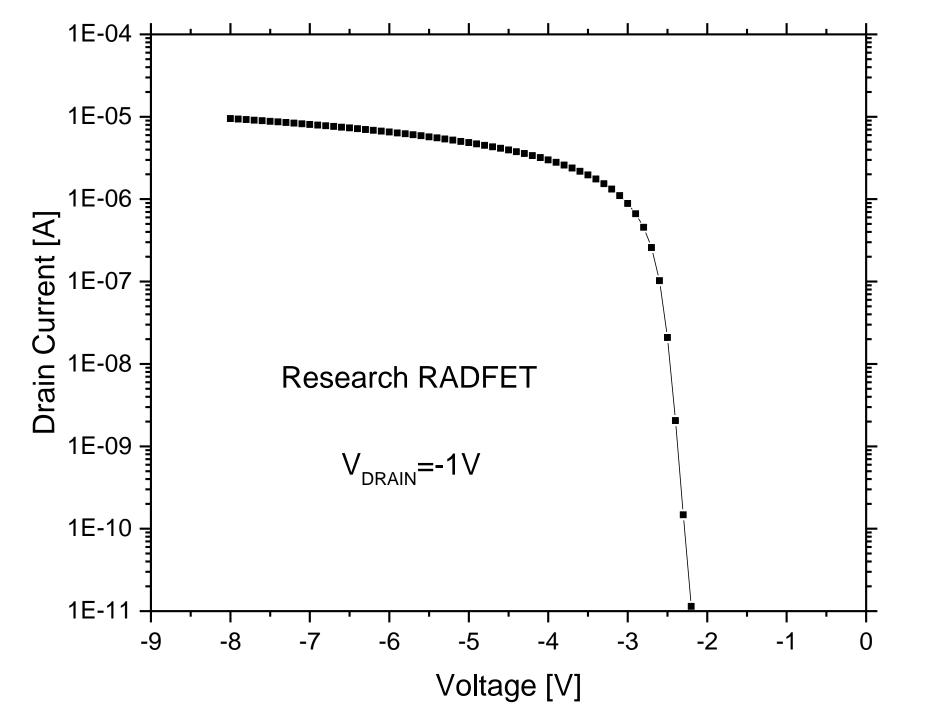

### **RADFET Current-Voltage Characteristics**

2<sup>nd</sup> ELICSIR School April 21<sup>st</sup> to 22<sup>nd</sup> 2021

2<sup>nd</sup> ELICSIR School April 21<sup>st</sup> to 22<sup>nd</sup> 2021

### **RADFET Temperature**

# **RADFET Current-Voltage Characteristics**

2<sup>nd</sup> ELICSIR School April 21<sup>st</sup> to 22<sup>nd</sup> 2021

# **Electrical Parameters across Wafer**

- Colour Map of electrical parameters

- Select areas of wafer for chip dicing and packaging

## Outline

2<sup>nd</sup> ELICSIR School April 21<sup>st</sup> to 22<sup>nd</sup> 2021

### 2<sup>nd</sup> ELICSIR School April 21<sup>st</sup> to 22<sup>nd</sup> 2021

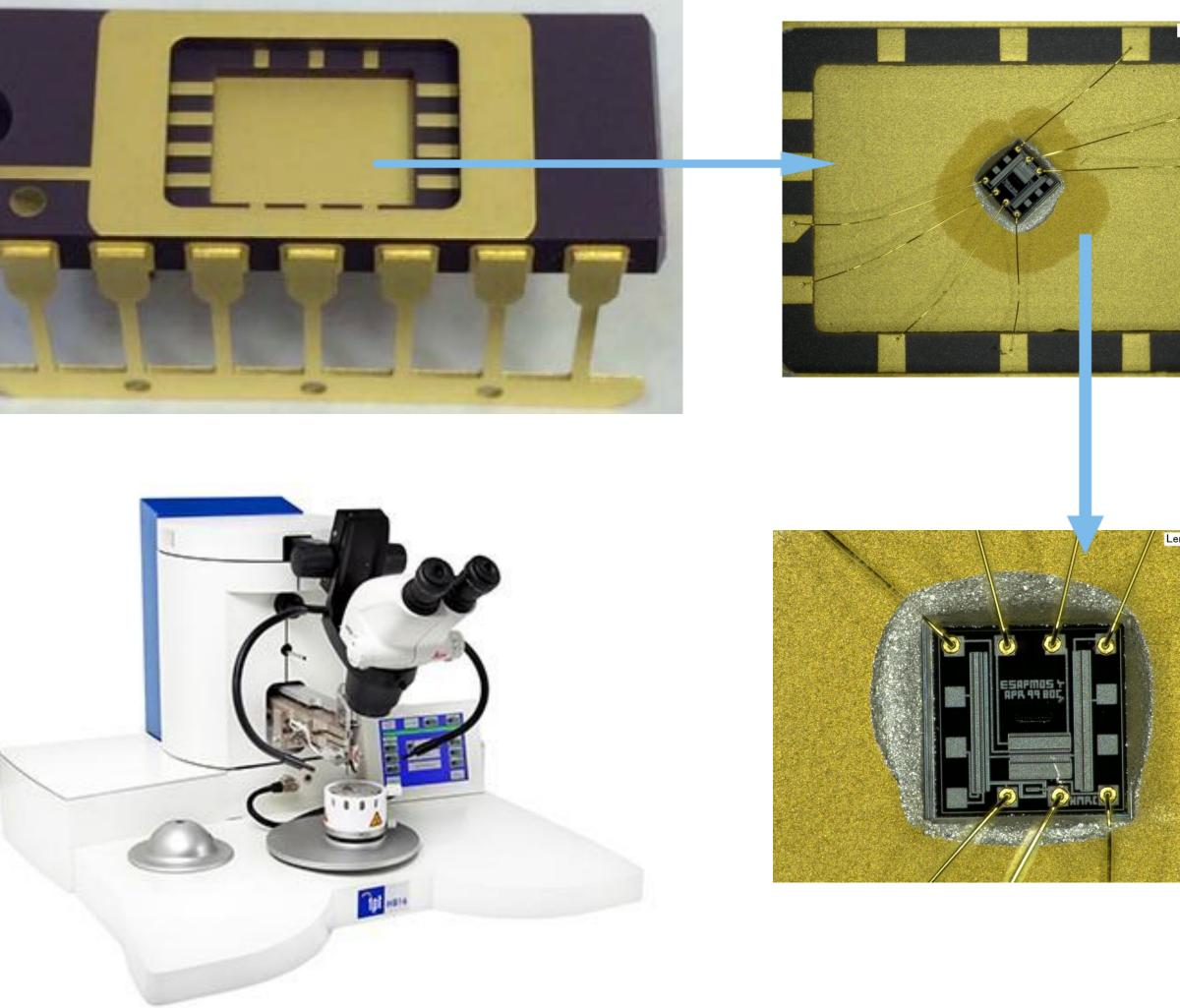

## Dicing of Wafer

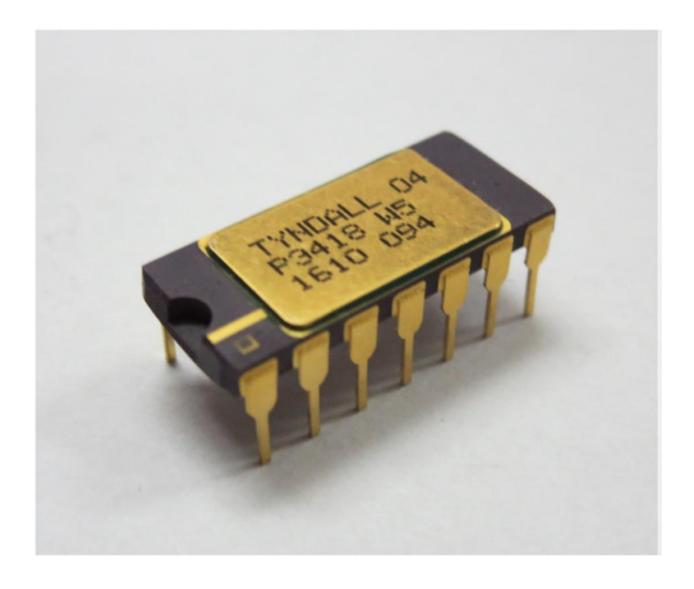

# Packaging Process

- Ceramic Dual in Line Packaging Types

- Gold wire bonds

- Thermo-compression

TPT Semi-automatic Wire-bonder

# Ceramic Packaging Lids

### • Kovar Lids are attached to package

- Same process as used for die attach

- 125°C maximum temperature

- Hermetic sealing subcontracted

- 300°C maximum temperature

- Package Dimension (LxWxH)

- 13mm\*8mm\*3mm

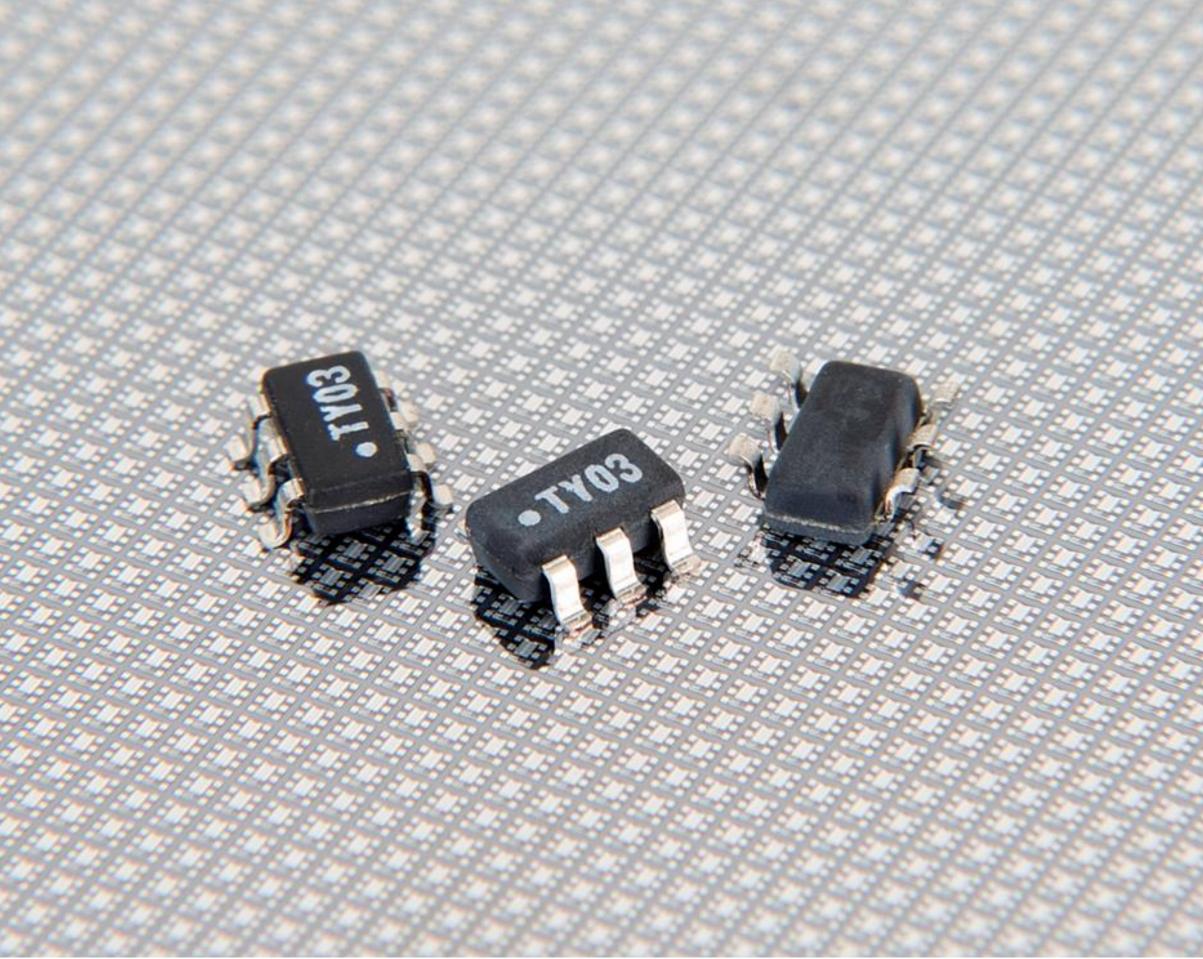

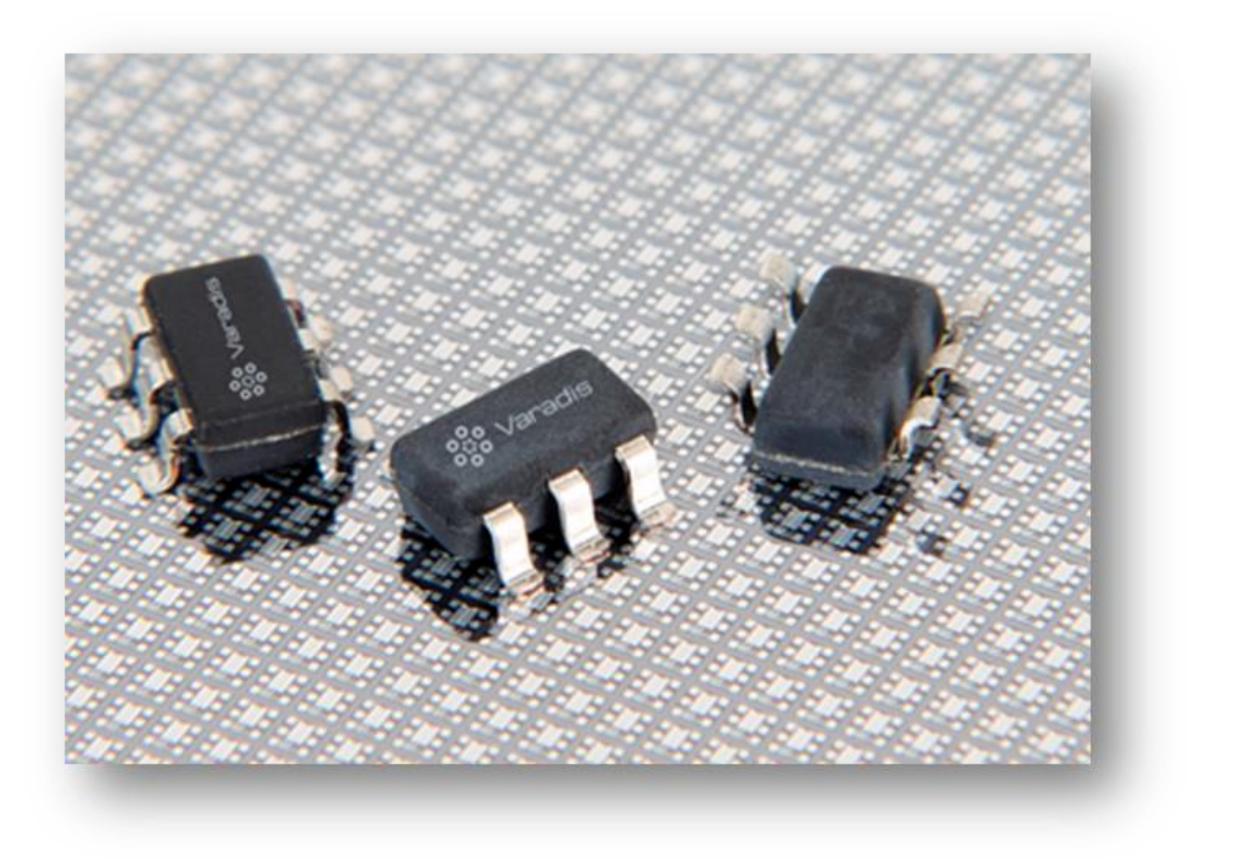

- SOT23 plastic package

- 3mm\*3mm\*1mm (LxWxH)

- 175C maximum temperature

- Thinning of silicon wafer required to fit into package

- 525µm thinned to 200µm

# **Plastic Packaging**

### Outline

2<sup>nd</sup> ELICSIR School April 21<sup>st</sup> to 22<sup>nd</sup> 2021

**RADFET Manufacture**

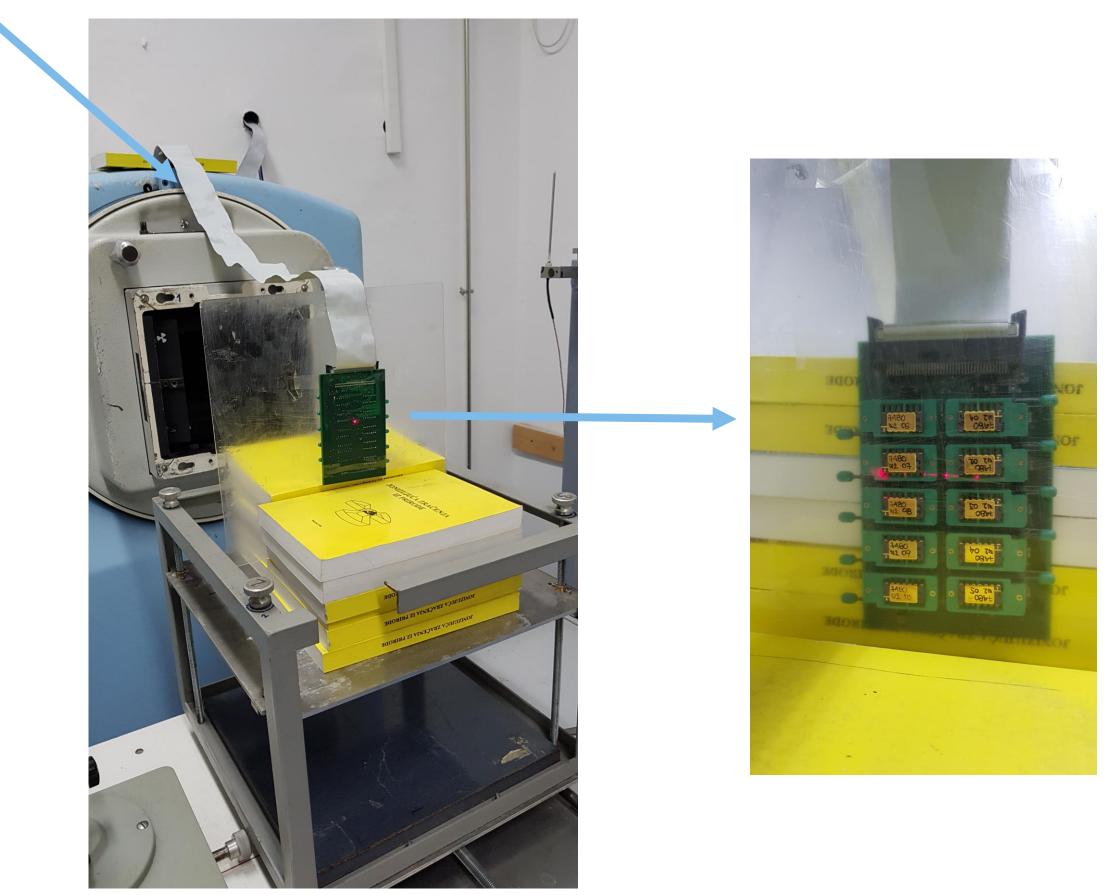

# **Product Testing**

- All products are first electrically tested using Keithley 4200 + test fixture

- Number of samples irradiated with Co60 source in Vinca, Serbia

- Automatic reader used to characterise a number of RADFETs simultaneously

### Flex Cable to Automatic Readout System

#### **RADFET Manufacture**

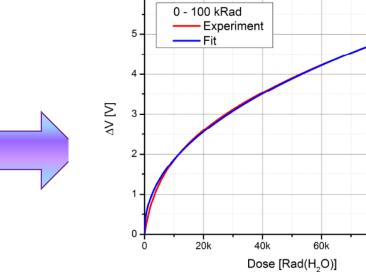

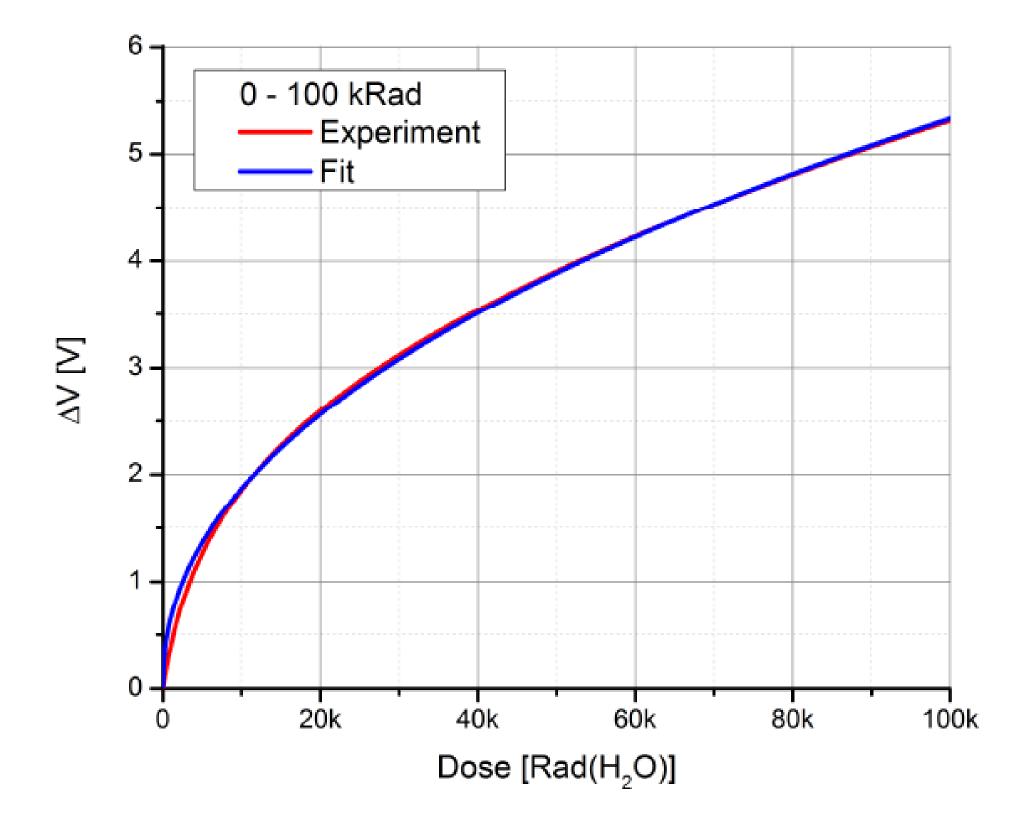

# Sensitivity Curve

- Mean Sensitivity Curve constructed from statistical data

- Parabolic Model fitted to Sensitivity Curve

$\Delta V_T = A \times Dose^B$

Model Fits sent to customer with product

**RADFET Manufacture**

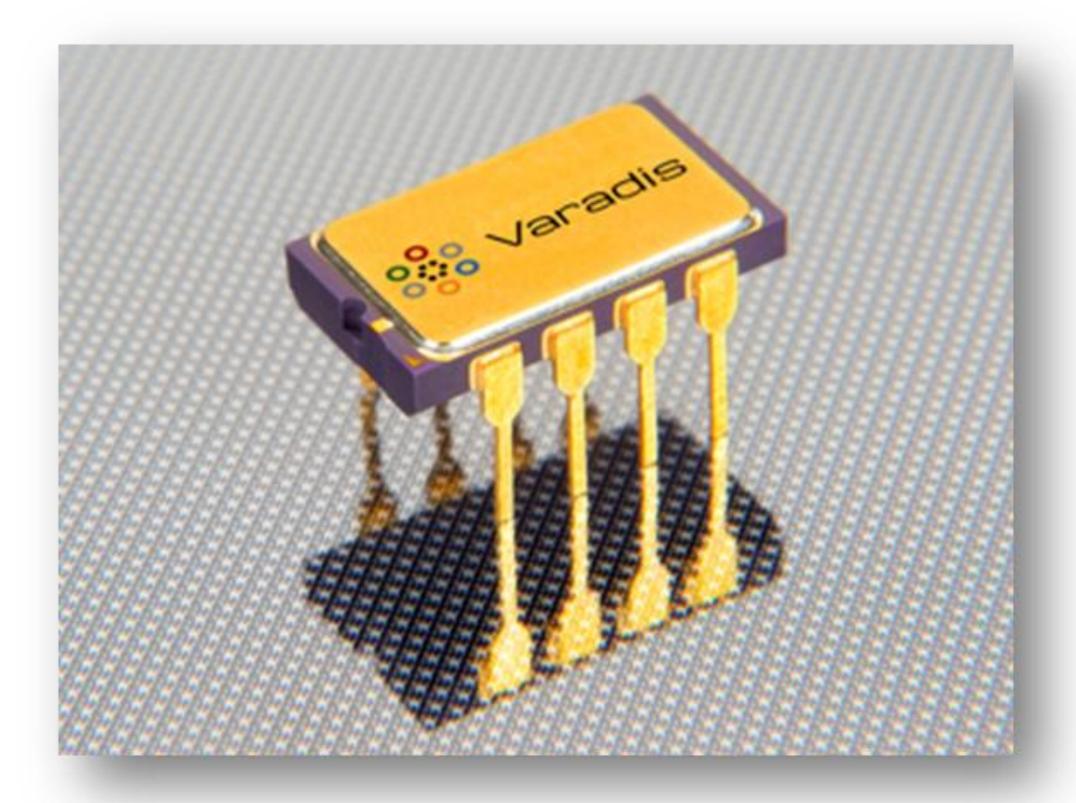

### Varadis Spin-out Company

http://www.varadis.com

2<sup>nd</sup> ELICSIR School April 21<sup>st</sup> to 22<sup>nd</sup> 2021

### Questions?

### E: <u>russell.duane@tyndall.ie</u>

### T: +353 21 2346201

Tionscadal Éireann Project Ireland 2040

European Union **European Structural** and Investment Funds